RTL

People often use the terms RTL and HDL interchangably.

I see it in a bit of a different way, influenced by Mead & Conway’s book “Introduction to VLSI systems”. It’s more of a design methodology.

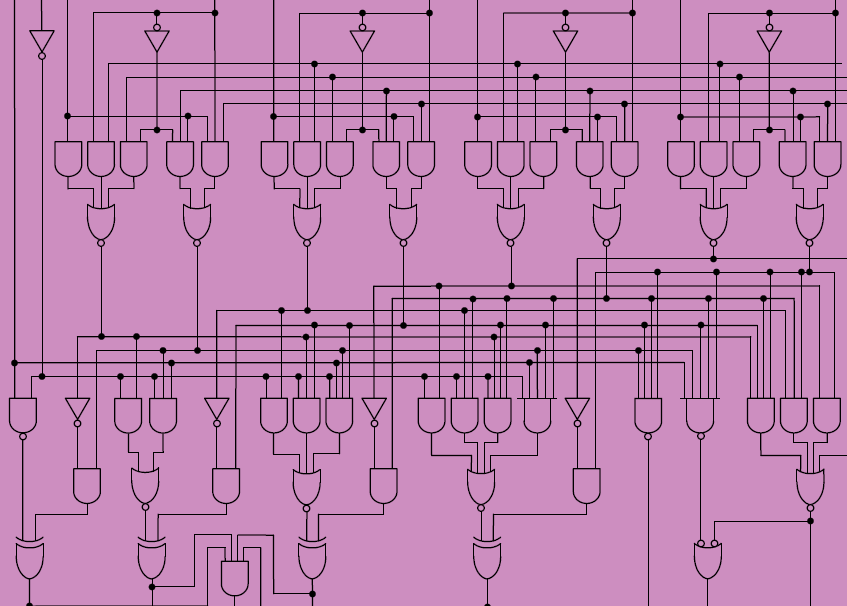

For reasons of speed and debugging, it makes sense to split up the data processing into smaller steps and buffer the results in registers (small memories usually made up of a stack of flip-flops). As the data flows between registers, it’s called register transfer level.

Here’s a quote from page 105 of the pdf of the book:

For a different viewpoint, this thread in stackexchange tries to answer the question - what is the difference between RTL and HDL.

I made a video about how flip-flops work, and cover a bit about the difference between combinatorial and sequential logic at the beginning.

Verilog and VHDL are both hardware description langauages (HDLs). They can describe all sorts of things, some of which are implementable by logic synthesis (ie synthesizable) and lots of things which are not. They can both describe netlists, ie the wiring together of pre-existing cells, and can also describe test harnesses and stimuli. The subset of these HDLs that is meant to describe real hardware behaviour (other than as netlist) is often referred to as RTL, but not all of this is synthesizable.

Course feedback

I took this course twice, and that probably means something! No, not what you're thinking—it means that beyond learning how to design, test, and tape-out your analog circuit, you gain access to the expertise of the best in the analog design community!

ReJ aka Renaldas Zioma (analog course)