Below you will find pages that utilize the taxonomy term “Interviews”

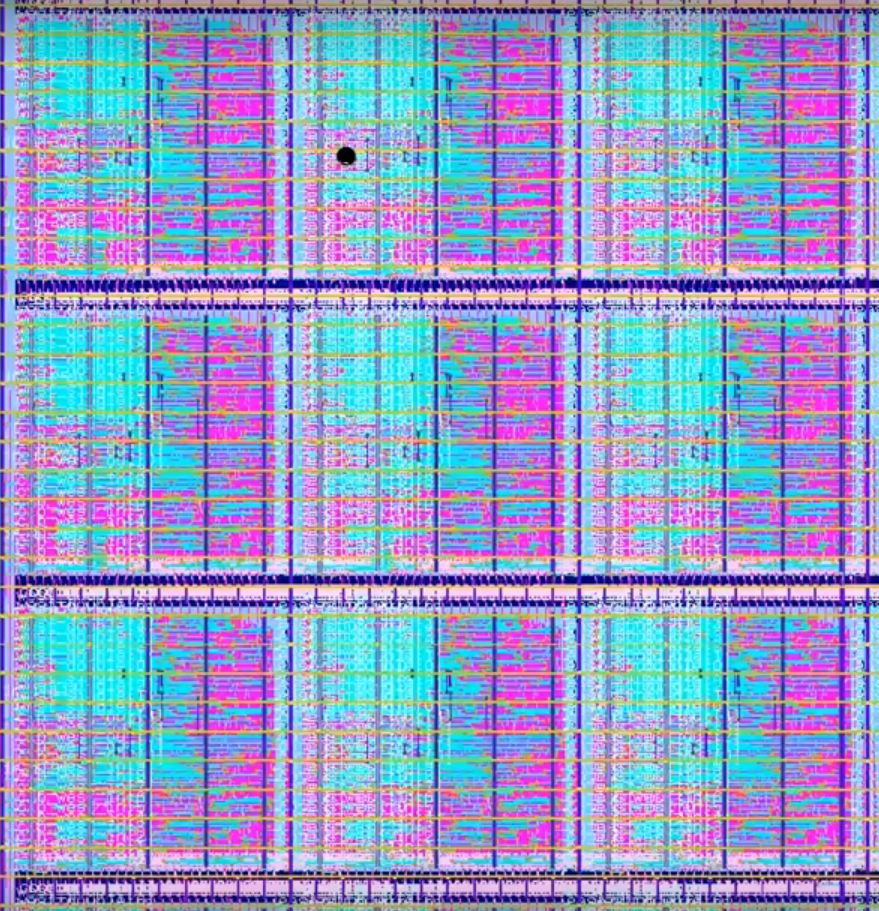

Looking inside an open source ASIC with Zeptobars

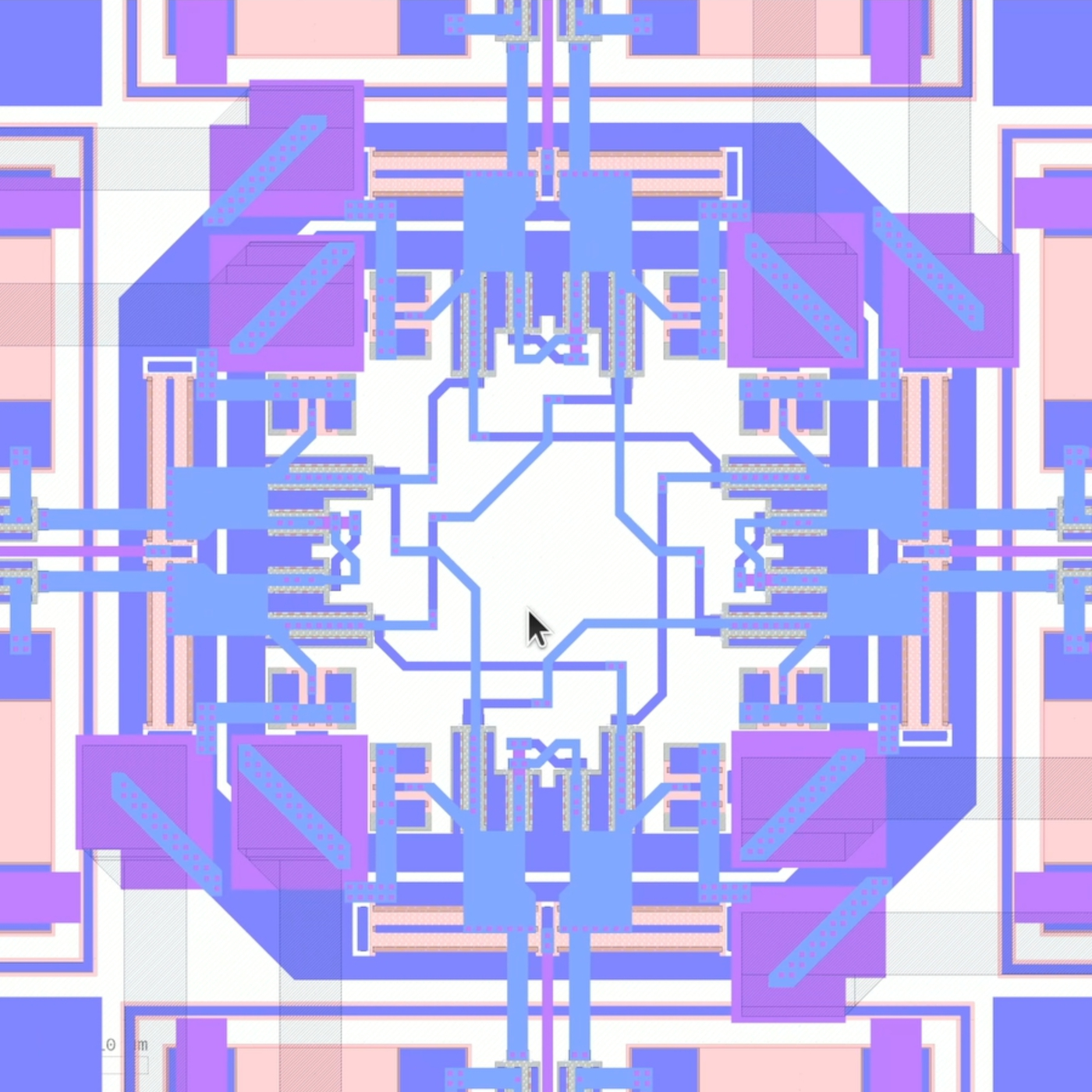

In this interview, I met up with Michael from Zeptobars in Zurich, Switzerland, where we use acid to decapsulate one of my Tiny Tapeout chips. This technique involves using acid to remove the protective epoxy layer of a chip, revealing the silicon die underneath. Decapping is commonly used to analyse the construction of integrated circuits. Michael usually decapsulates chips designed by others, sometimes decades ago, but this time one of the designs is his own.

Analog Philosophy with Carsten Wulff

In this insightful interview, I talk with Carsten Wulff, Principal IC Scientist at Nordic Semiconductor, about all things analog ASIC design.

Carsten kicks things off by sharing a fascinating anecdote about how he ended up designing an analog SAR during his winter holiday in the Norwegian mountains, sparked by the opportunity to include analog designs on Tiny Tapeout 6.

The conversation then shifts to Carsten’s thoughts on the accessibility of 130nm technology for analog design, which he believes is “the last comfortable node”. While larger designs with millions of digital gates might not be suitable, 130nm shines for analog applications, offering a sweet spot between performance and cost-effectiveness.

Free Silicon Conference 2023

The Free Silicon Conference returned to Paris in 2023. There were plenty of great talks and I really enjoyed the conference. I was able to interview the organiser and several speakers:

- Luca Alloatti - organiser

- Thomas Benz - PULP

- Jørgen Kragh Jakobsen - his work on open source silicon in Denmark

- Thomas Parry - startup founder of Spherical Systems

- Rene Scholz - Open source PDK from IHP Microsystems

- Dan Fritchman - Analog tools

- Harald Pretl - Mixed signal design

You can find all the recorded talks here.

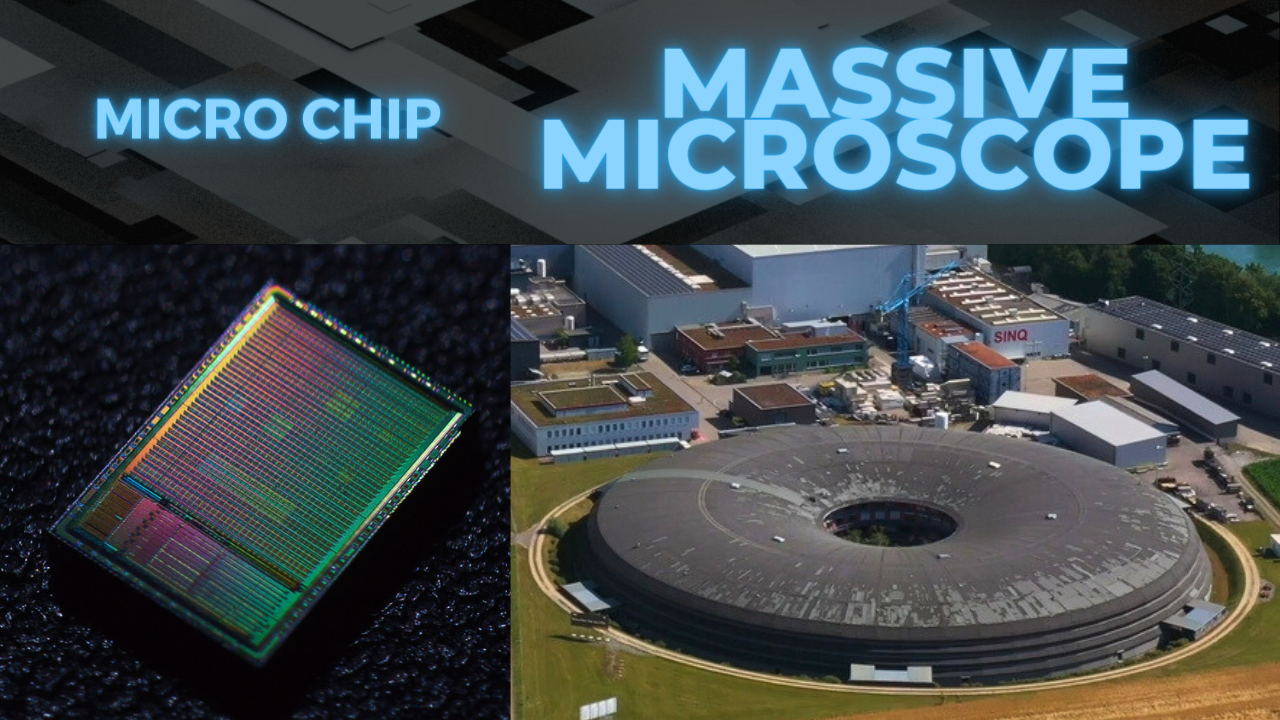

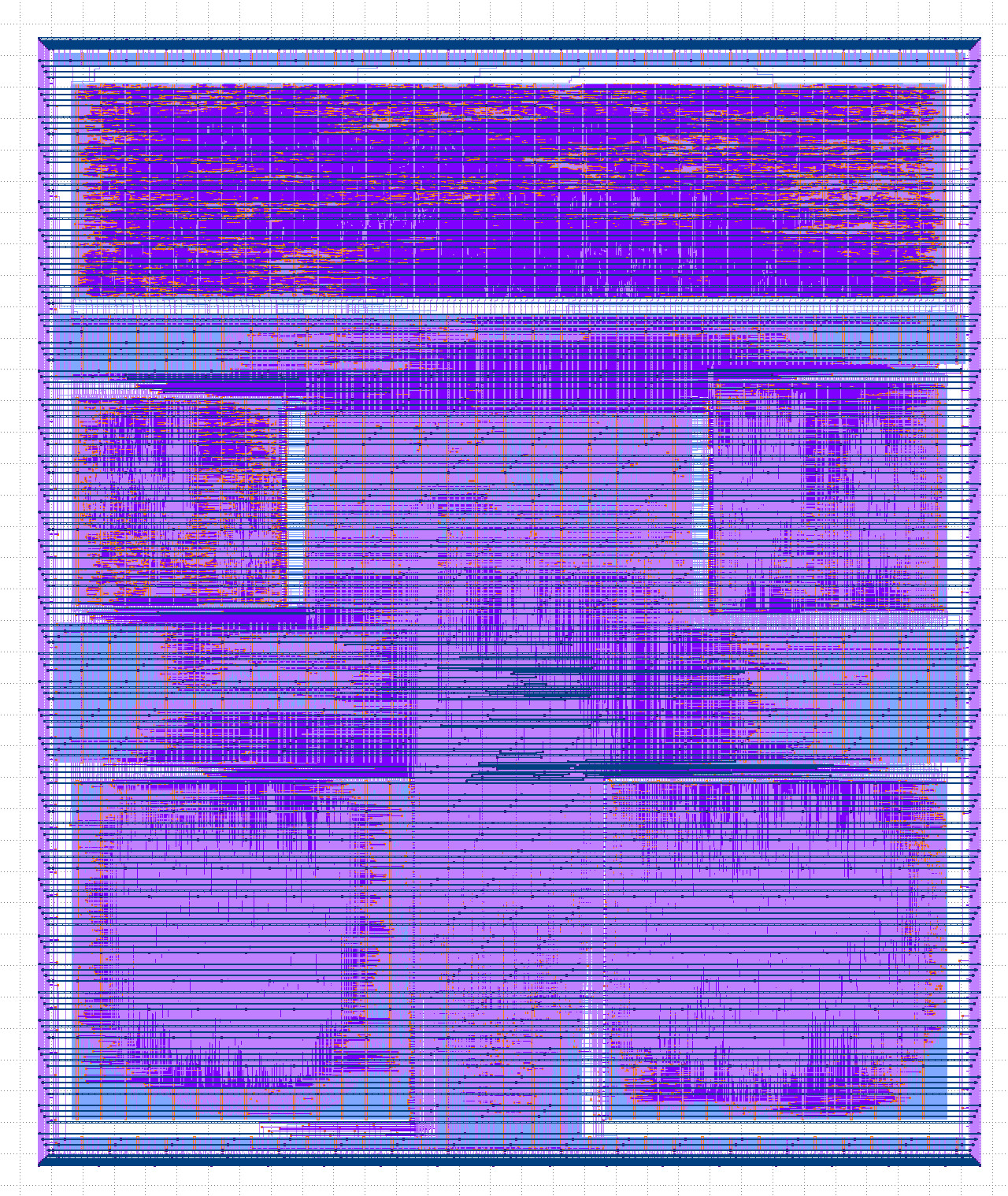

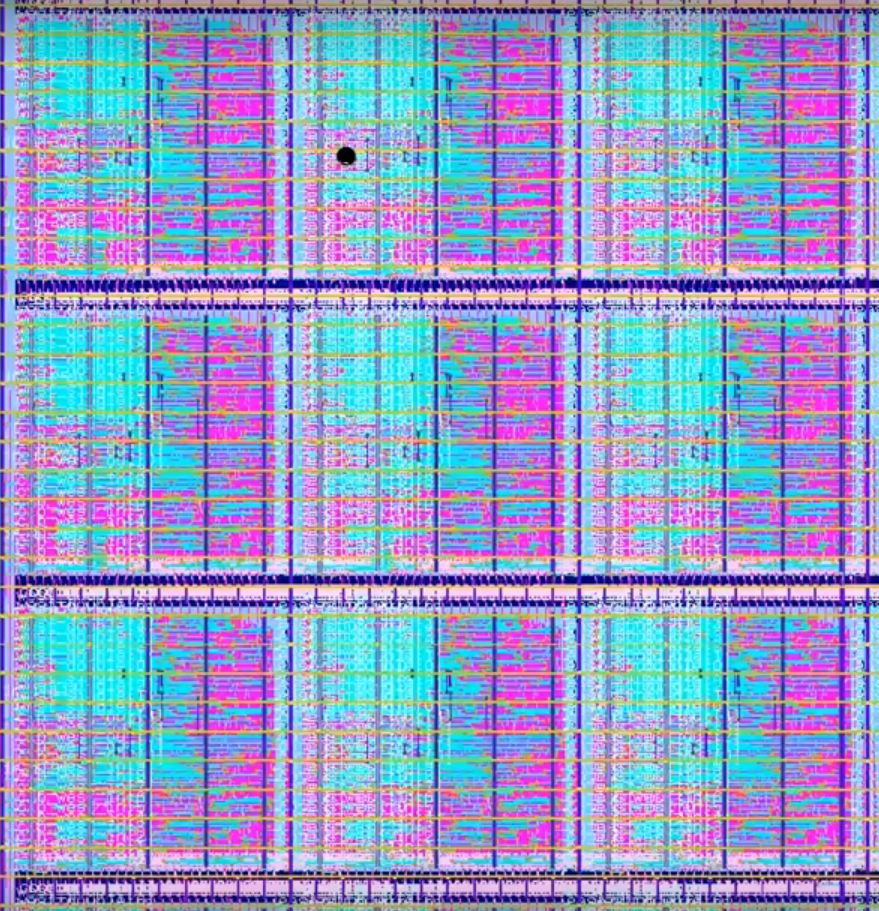

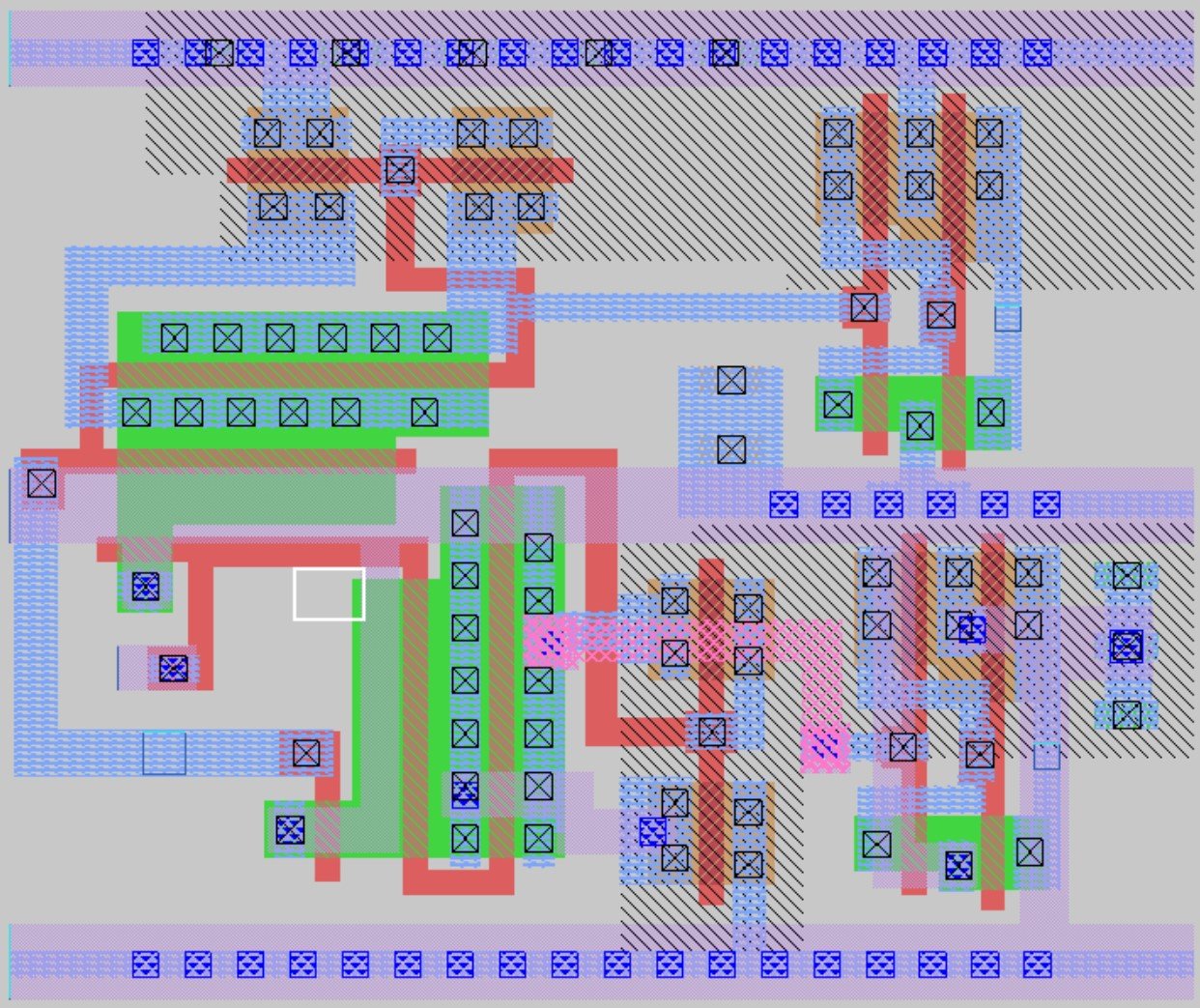

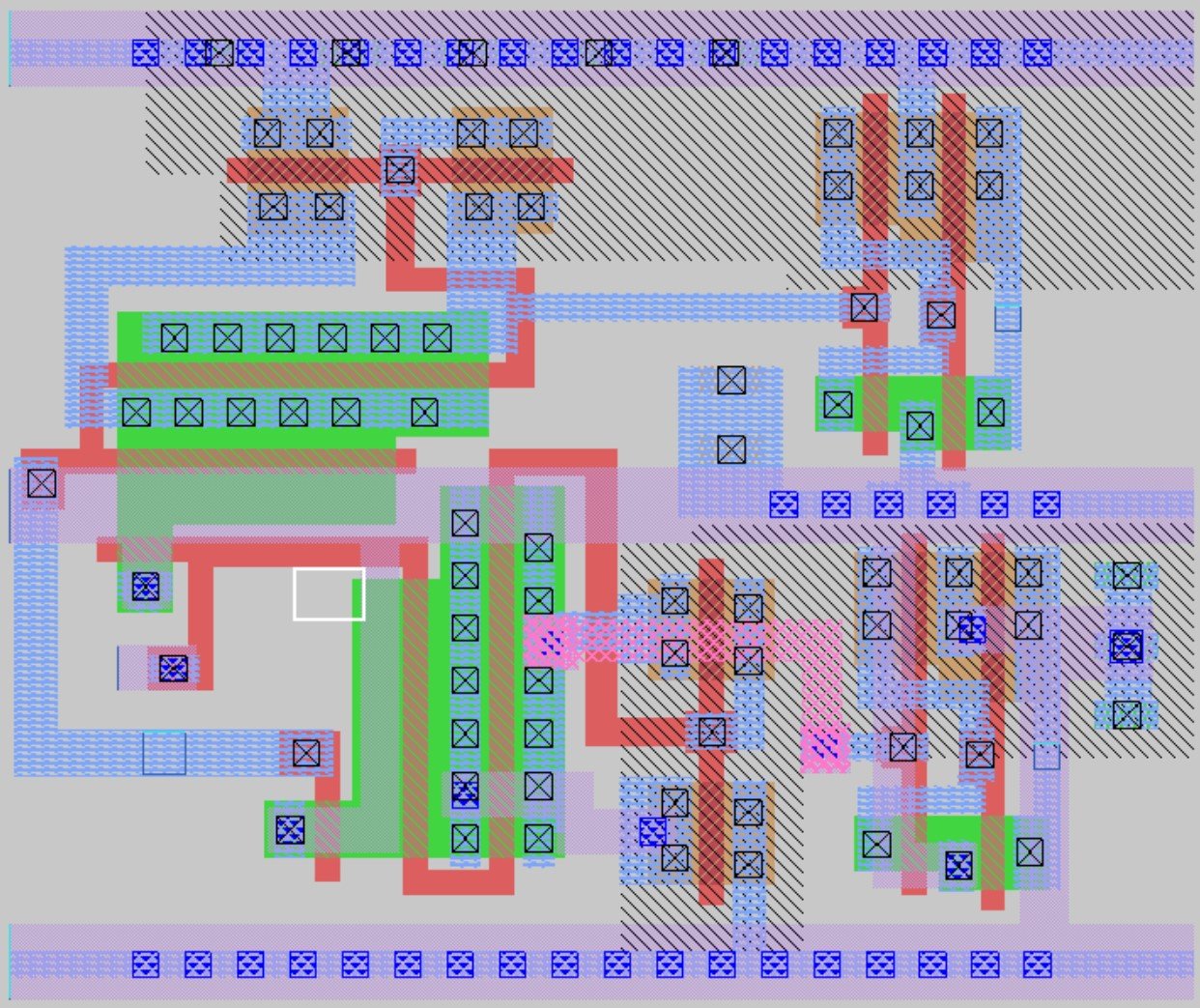

Looking inside my first ASIC with a particle accelerator

I got a once in a lifetime chance to use a particle accelerator to look inside my first ASIC!

It was amazing to be able to see all the different layers and match them up with the design files I sent to Efabless.

So join me on my journey to the Swiss Light Source at the Paul Scherrer Institut where I learnt how they use their synchrotron to make some awesome images!

I also have a public photo album if you want some SLS themed wallpaper!

The MOnSter 6502 - a 6502 processor out of discrete transistors

I had the chance to interview Eric Schlaepfer about his MOnSter 6502, a 6502 processor made out of discrete transistors. For me, one of the most interesting things about this project are the similarities to ASIC design, for example Eric wrote his own LVS tool.

You can find out lots more at his website.

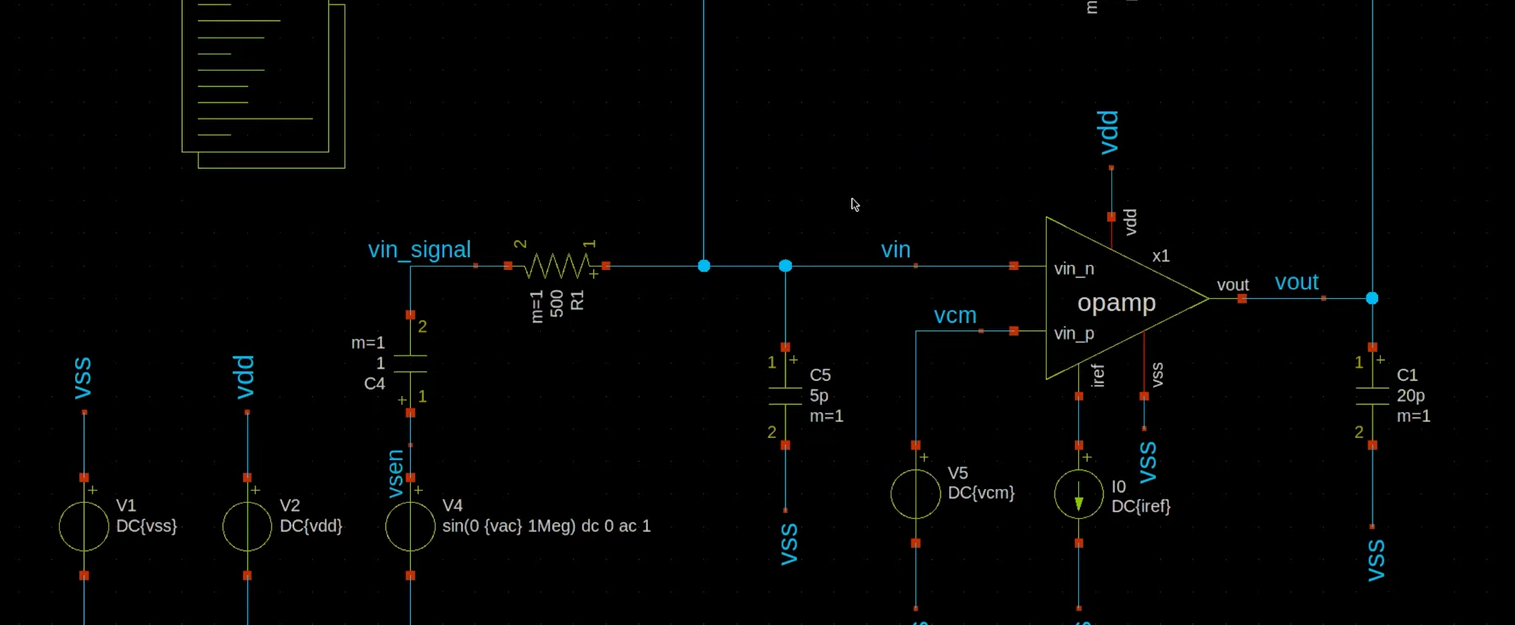

Analog with Digital Standard Cells

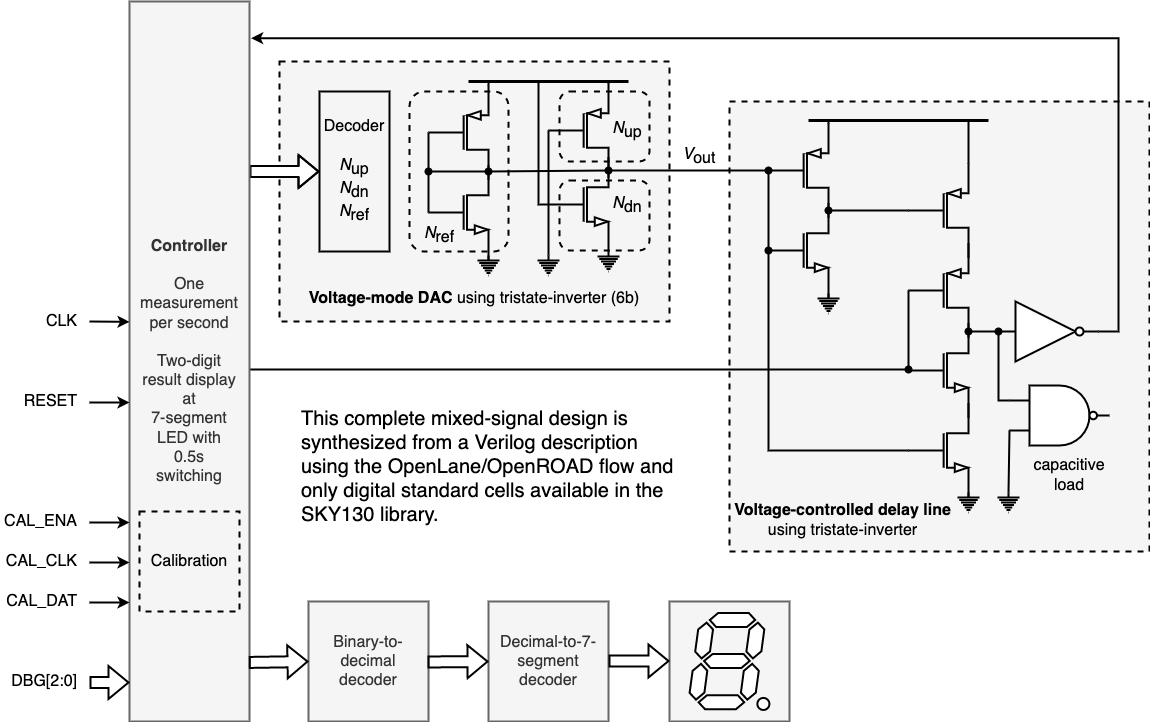

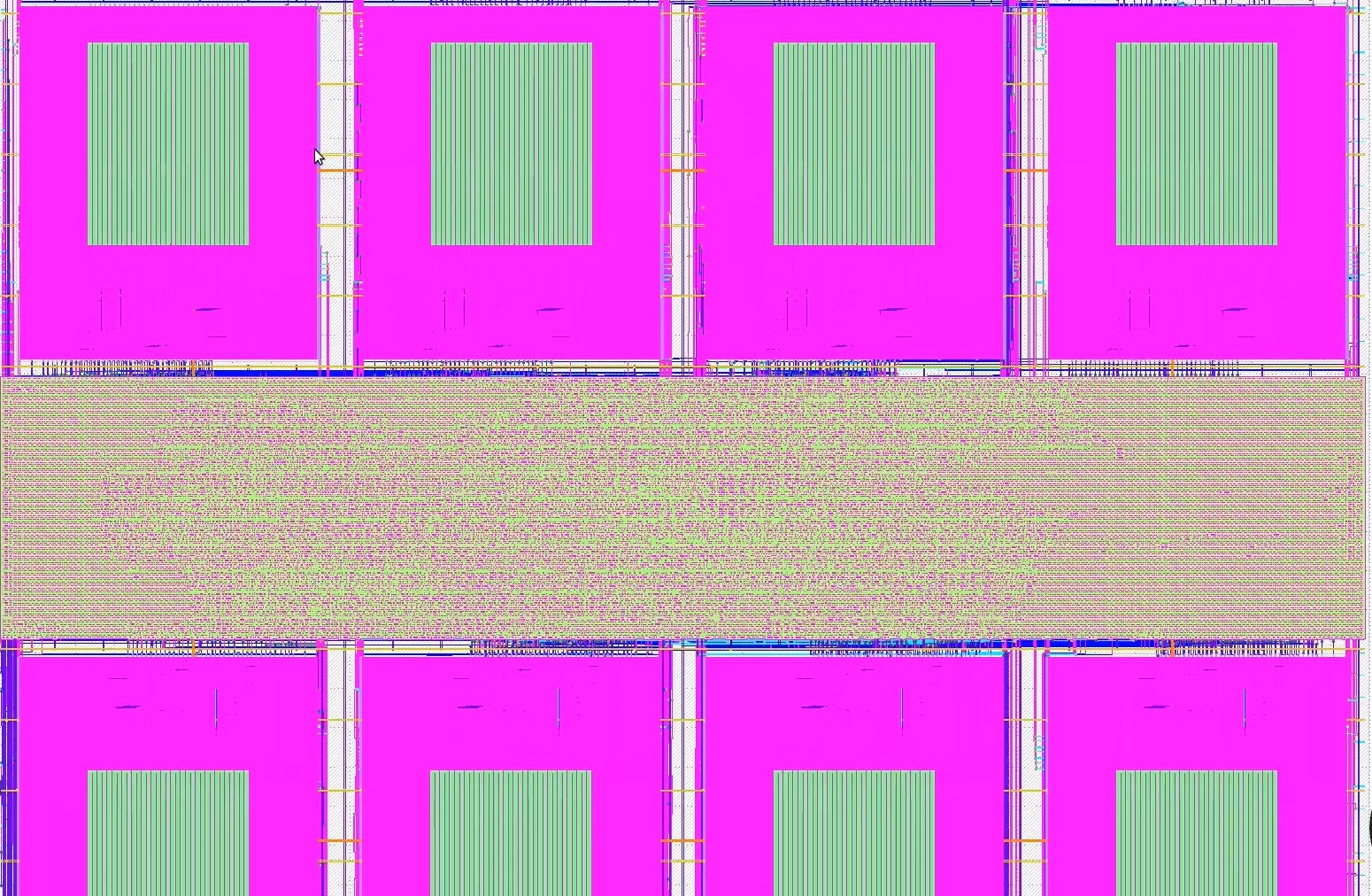

Harald Pretl made a fascinating submission to Tiny Tapeout 3, an analog circuit made from digital standard cells.

It builds a DAC out of a lot of tristate inverters, and a big capacitor by ganging up a lot of NAND gates.

In this interview with Harald we discuss how it works and how he made it and simulated it.

You can check his design here, including the source and GDS.

Interview with James Stine - Open Source Standard Cells

In this interview with Professor James Stine, we talk about:

- Why is Open Source the key to innovation?

- What do students struggle with most when learning to design standard cell libraries?

- What are the biggest misconceptions engineers have about standard cells?

- What’s James’ tool flow?

- How many cells are needed to make a library?

- Why do we need another library for Global Foundries (GF) 180?

- How far are open source tools from commercial tools?

- Could automated layout of standard cells compete with hand layouts in nanometer processes?

- With Moore’s Law slowing down, do any circuit families deserve a second chance?

- Why would nVidia make a 7.5T standard cell library?

Text of the interview is included below.

ASIC Development in the Cloud

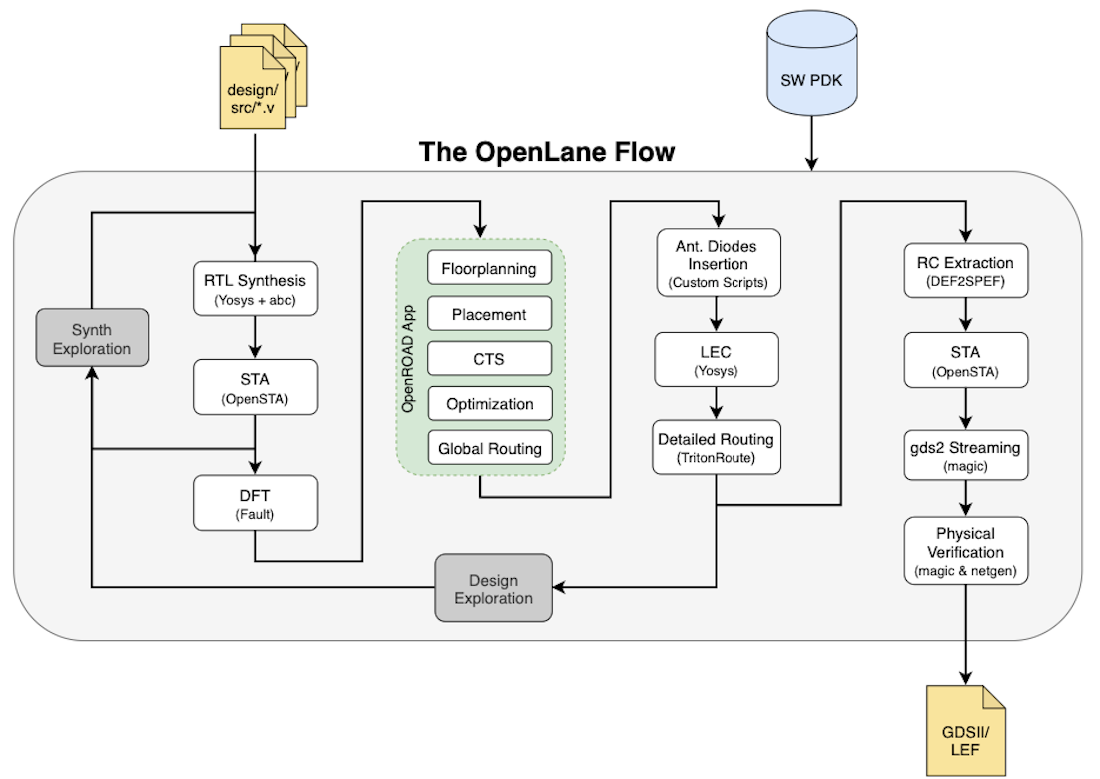

Proppy has been doing some great work with preparing the open source ASIC tools to work inside Jupyter notebooks. This means that you can now experiment with simulation and ASIC hardening without needing to download or configure the tools.

I think this is going to be of great importance for academia and education:

- Now when people publish papers they can include a link to a notebook that reproduces the published results.

- For education, it’s going to be so much easier to do a class workshop without having to install tools or maintain VMs.

Proppy demonstrated and explained his work in this interview.

Interview With Teo

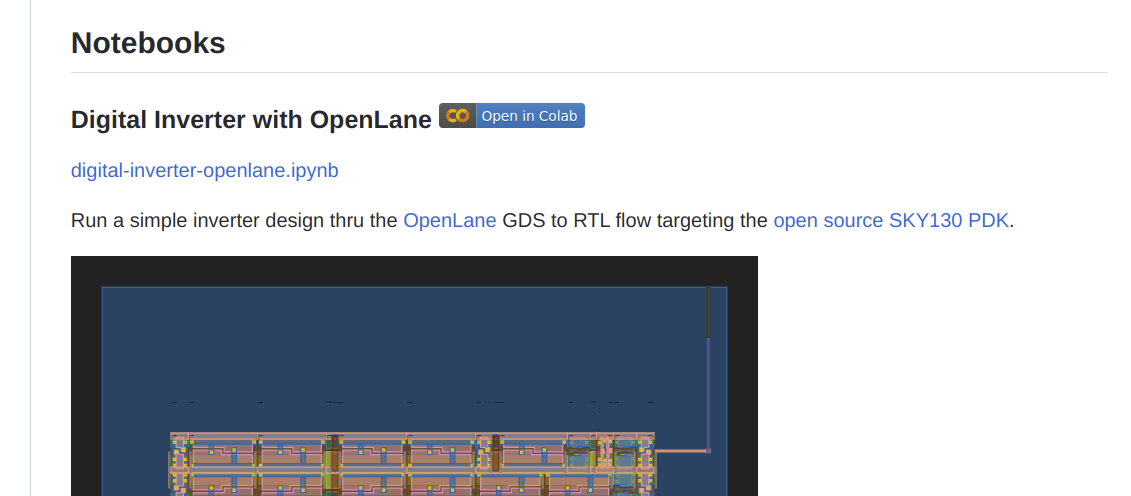

Teodor-Dumitru Ene has been doing some interesting work on optimising hardware adders. Until I spoke with him, I didn’t realise how important this basic digital building block really is. An interesting statistic from his presentation slides:

When a RISC-V processor boots into Linux, 65% to 72% of instructions use addition.

By default, Yosys will synthesise something like this:

reg [31:0] a;

reg [31:0] b;

wire sum = a + b;

Using a ‘middle of the road’ adder, that gives medium PPA (power, performance, area) results. Teo has made a Python library and Yosys plugin that allows us to choose between 4 other types of adder:

Interview With Matt Guthaus

In this interview with Matt Guthaus, we talk about:

- Recap - what is OpenRAM

- Why do we need a memory compiler like OpenRAM?

- 3 phases of OpenRAM development

- What’s changed since FOSSi dialup

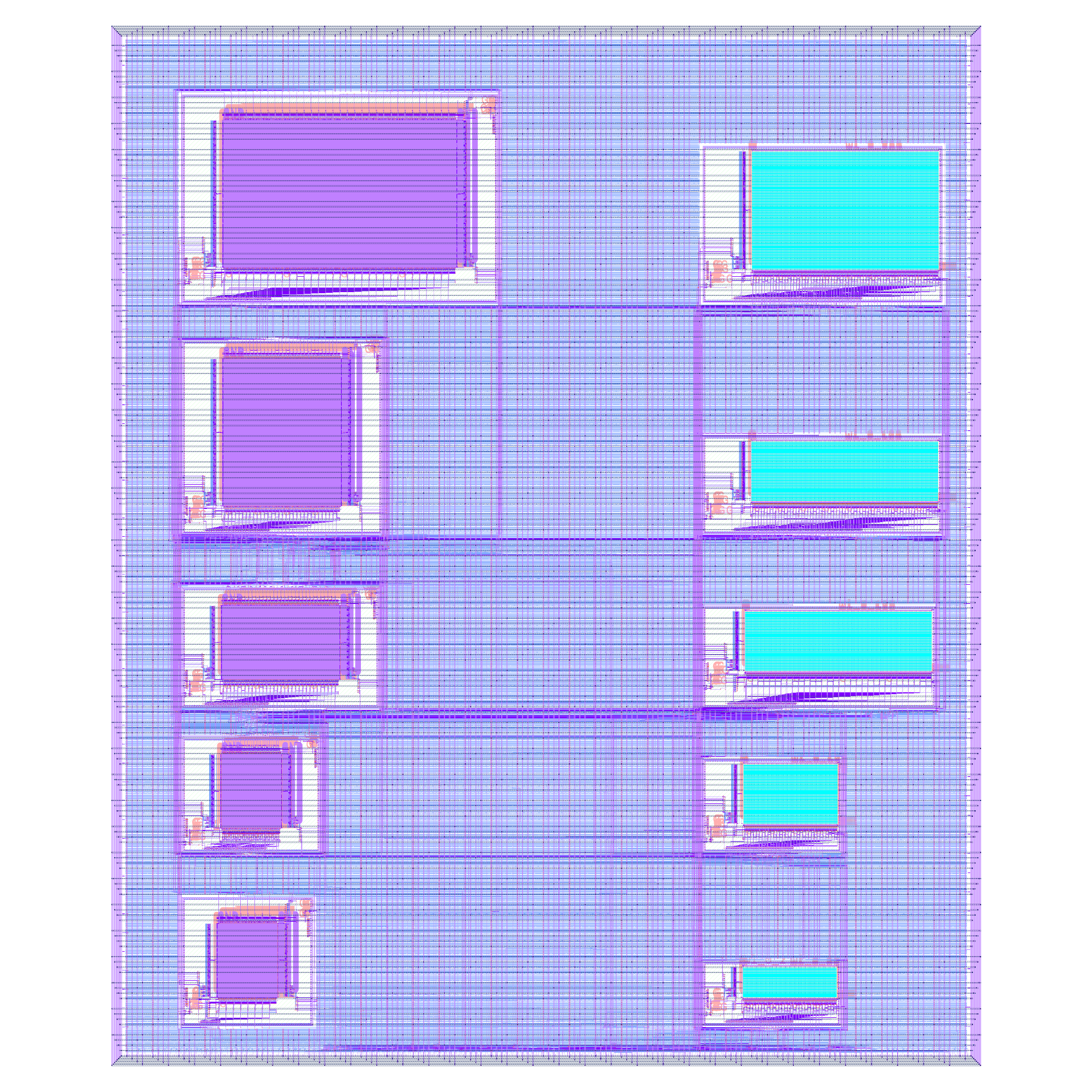

- MPW2 tapeout of OpenRAM

- Test modes

- What was hard about MPW2

- DRC issues

- Status of OpenLANE support for OpenRAM

- Future plans for OpenRAM

- Access to resistive RAM, hopefully for MPW4

Resources

- WOSET link: https://woset-workshop.github.io/

- MPW2 application: https://platform.efabless.com/projects/187

- FOSSi dialup on OpenRAM: https://www.youtube.com/watch?v=9Lw83kFtnc4

Interview With Tom Spyrou

Tom Spyrou is a long time EDA developer who has worked at large and small companies.

- In 1988 Developed QTV at VLSI technology. It was the first STA engine to be trusted to sign off devices for fabrication without timing based simulation.

- He was the original architect of PrimeTime STA algorithm.

- Manager of Cadence Common timing Engine and precursor to Open Access

- Senior technical positions at Synopsys, Cadence, Simplex, AMD, Altera and Intel.

Since 2019 he has been the Chief Architect and Technical Project Manager of OpenROAD since 2019.

Interview With Dirk Koch and Nguyen Dao

One of the popular types of entries to MPW1 & 2 have been FPGAs. I have previously spoken with Arya Reais-Parsi about their FPGA project submitted to MPW1.

In MPW2 I noticed there were a couple of applications that seemed fairly advanced - especially FuseRISC: 2 RISCV processors with embedded FPGA fabric between them.

Dirk & Nguyen kindly allowed me to interview them about:

- their FABulous eFPGA framework,

- support for Yosys & NextPNR,

- parameterisation of the fabric,

- blockrams with OpenRAM,

- their MPW applications and previous tape-outs, and

- their experience with the open source tools.

Enjoy!

Livestream with Thomas Parry: analogue design with the open source ASIC tools

There continues to be a lot of interest about analogue design with the open source PDK.

To cover this interest, I’ve previously interviewed:

One of the big changes in MPW2 was the provision of more analogue support in the form of Caravan - a new harness. This is exciting because one of the key advantages of an ASIC over an FPGA is the mixed signal capability.

Interview With Dan Rodrigues - first shuttle, racing the beam & retro gaming

In this interview Dan and I talk about his submission to the first shuttle, simulating video projects, how to do graphics with no frame buffer and the joys of retro gaming.

- Caravel repo: https://github.com/dan-rodrigues/caravel_vdp_lite

- IceStation32: https://github.com/dan-rodrigues/icestation-32

Interview With Thomas Parry - Amateur satellite radio, Open Source vs Industry tools and beautiful analogue layout

In this interview Thomas talks us through his Amateur satellite transceiver shuttle submission. We also discuss the differences between the Open Source tools and the industry standard ones he uses in his day job.

- Design repo: https://github.com/yrrapt/amsat_txrx_ic

- Caravel repo: https://github.com/yrrapt/caravel_amsat_txrx_ic

- Connect with Thomas on linkedin: https://www.linkedin.com/in/thomas-parry-60419468/

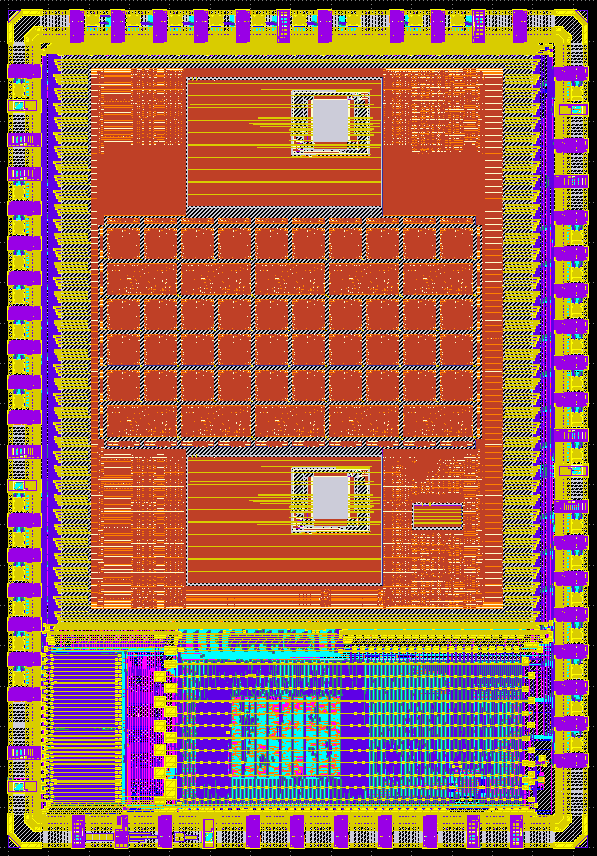

Interview With Anton Blanchard - Microwatt: a 64 bit OpenPOWER core, VHDL and OpenLane

I interviewed Anton Blanchard about his MPW1 application - a 64bit OpenPOWER core written in VHDL.

We talked about:

- VHDL vs Verilog

- FPGA vs ASIC

- Problems they faced with such a big design

- SRAM vs DFFRAM

- Software vs Hardware mentality

- Fixing bugs and contributing to OpenLane

You can check out the repository here: https://github.com/antonblanchard/microwatt-caravel

Interview with Tim Edwards - what happens between ASIC submission and sending to Skywater?

In this interview I talk with Tim Edwards from eFabless. He is their vice president of analog and platform.

We mostly talked about what needs to happen before they send the final files to Skywater.

A lot of the work is infrastructure:

- fetching files,

- compositing IDs,

- generating fill layers,

- a final DRC run.

Interview with Lakshmi S - PLL design

In this interview I talk with Lakshmi S about their shuttle submission.

As well as convering what a PLL is and its component parts, we also answered some interesting questions from the twitter community:

- how long things take to design, what is fun and what is frustrating,

- how to change the PLL’s response,

- why design a integrated loop filter,

- process corners and ngspice

- post silicon testing.

The repository is here.

Interview With Diego Hernando

In this interview I talk with Diego Hernando about their ASIC submission.

They have been working on some analog blocks; mostly op-amps but also including a PLL from another designer.

We discuss the difference between digital and analog design, the tools, simulation, layout and testing.

Here’s the link to the repository

Interview with Arya Reais-Parsi - FPGA fabric

In this interview I talk with Arya Reais-Parsi about their shuttle submission. They are working with a group of students to create Open Source FPGA fabric that can be put on an ASIC and configured with yosys/nextpnr.

The repository is here.

Interview With Sylvain 'tnt' Munaut: USB peripherals

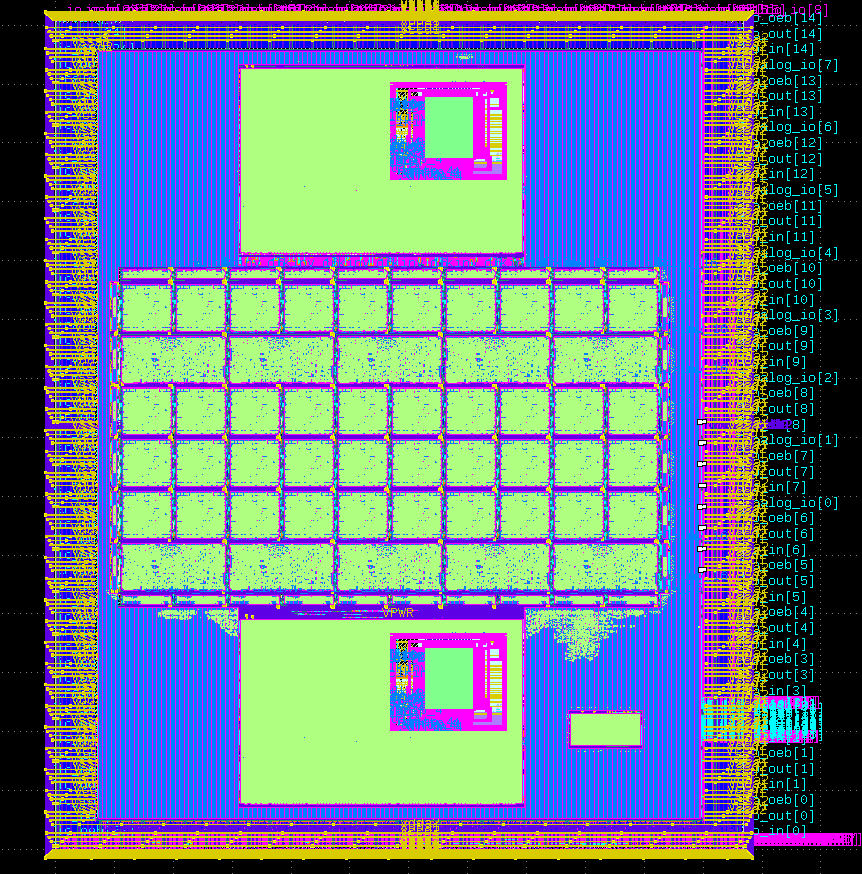

In this interview I talk with Sylvain ’tnt’ Munaut about his Google/Skywater ASIC application.

The design is especially interesting to me because of the way it merges the SRAM blocks with the logic. This has been a major challenge in my own design.

Here’s the link to the repository

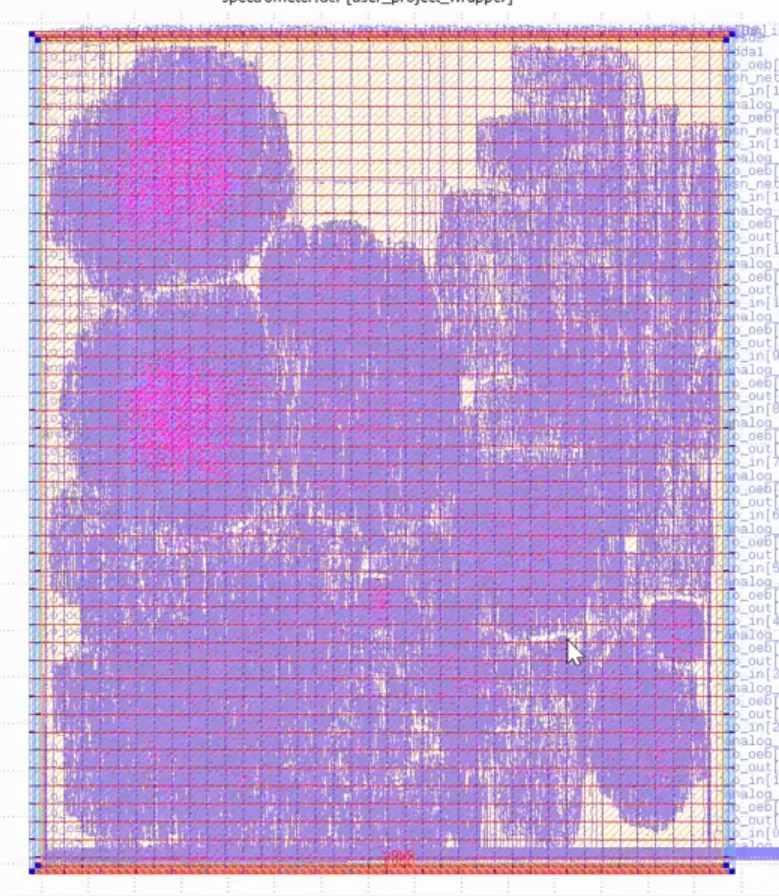

Interview With Vladimir Milovanović - spectrometer with Chisel

In this interview I talk with Vladimir Milovanović about putting a spectrometer on the Google/Skywater/Efabless ASIC shuttle.

He created the design using Chisel.

The repository is here.