Below you will find pages that utilize the taxonomy term “Videos”

Celebrating 20k YouTube Subscribers

Since I started my channel in December 2020, I’ve posted 181 videos that have been watched 660k times for a total of 35k hours! To celebrate reaching 20k subscribers I wanted to share some of the ones I’m especially proud of, and why they matter to me.

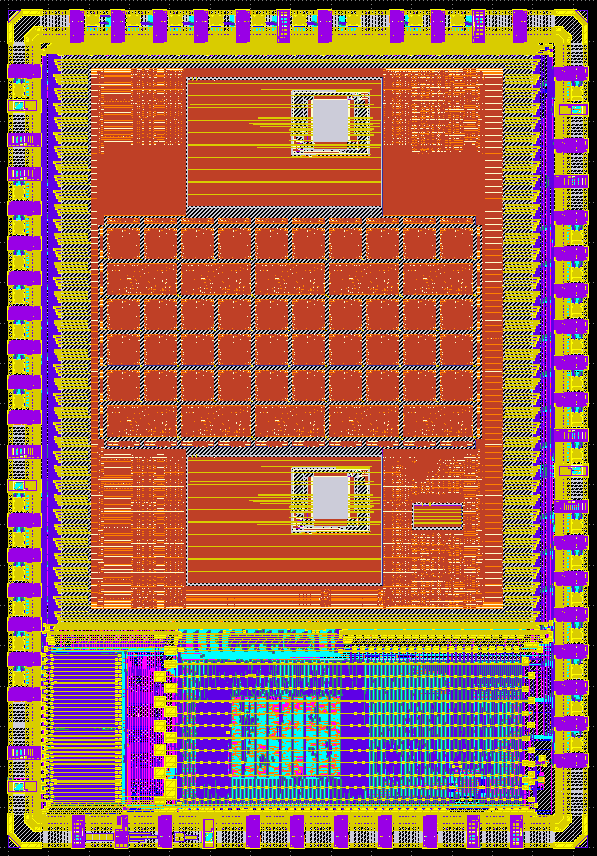

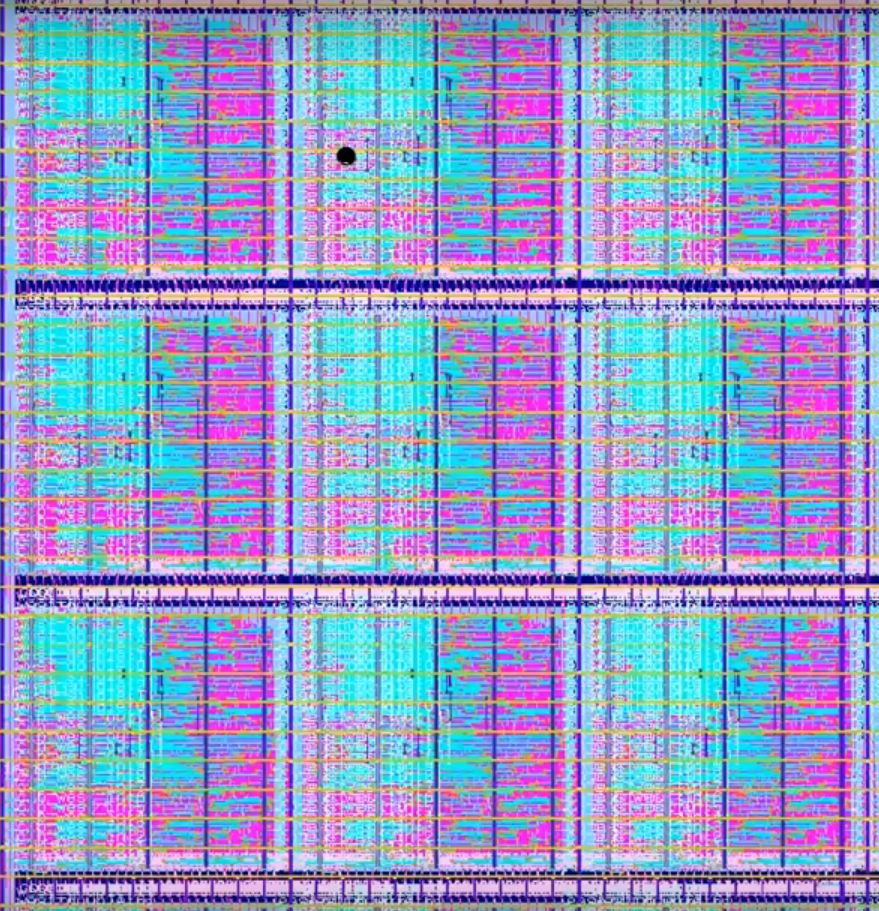

I’d say my all time favourite was when I used a particle accelerator to look inside my own microchips!

I met Tomas Aidukas at the Free Silicon Conference. In his talk, he showed an amazing 3D view inside a microchip - captured using a technique called ptychographic X-ray computed tomography. I asked if he’d be interested in imaging one of my open source chips. It turned out that having the source files for the chip was actually pretty unique.

Get started with open source ASICs

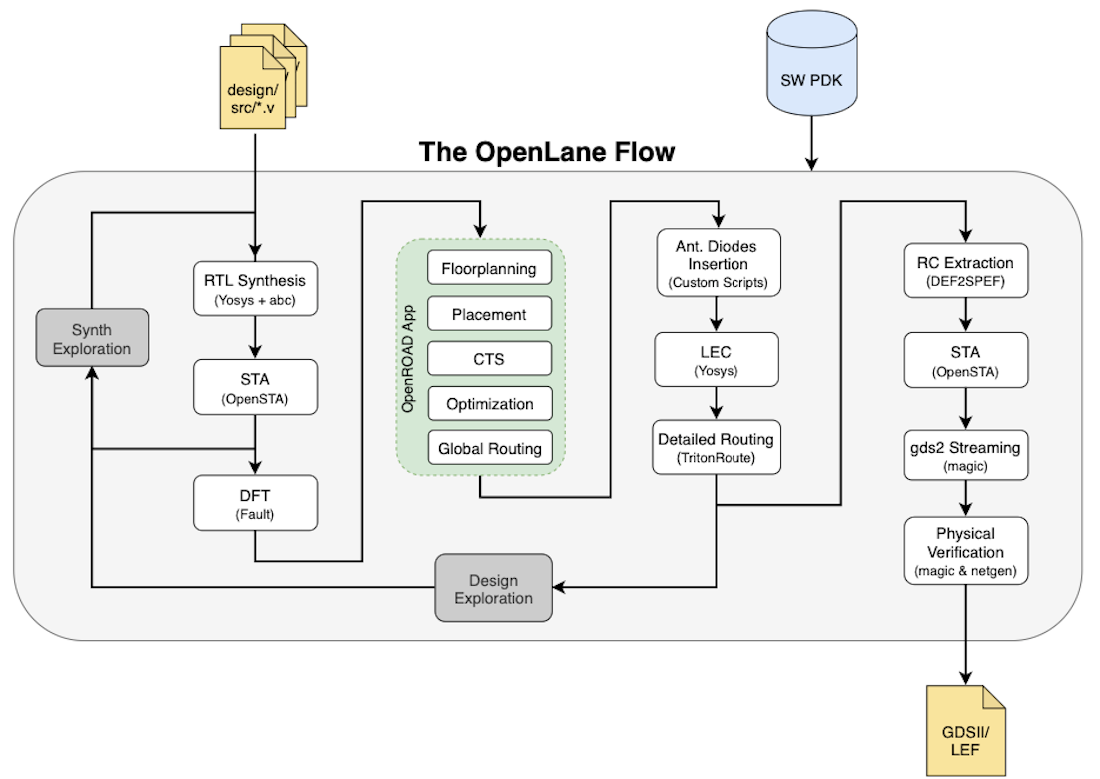

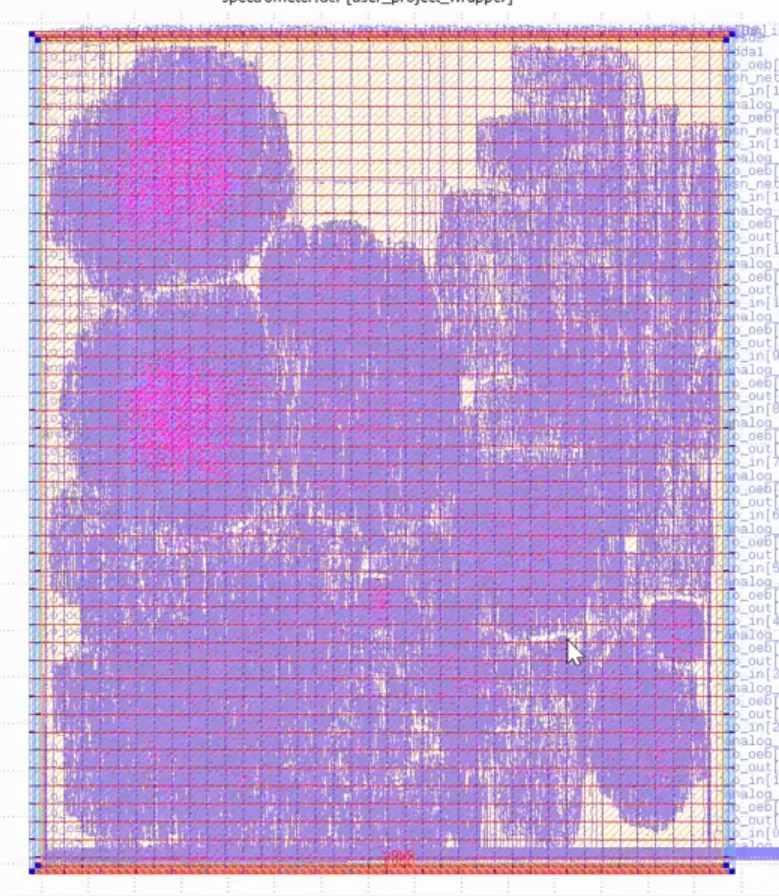

In my recent video Getting started with open source ASICs, I provided an overview of the open-source silicon movement, highlighting key resources and tools while showcasing some inspiring projects.

The video starts by looking back at the game-changing moment in 2020 when Google, Tim Ansell, and Efabless announced their free shuttle program, making it possible for anyone to get their open-source chip designs manufactured. This sparked a wave of innovation, with many taking their first steps in ASIC design using open-source tools like OpenLane and the Skywater 130nm PDK.

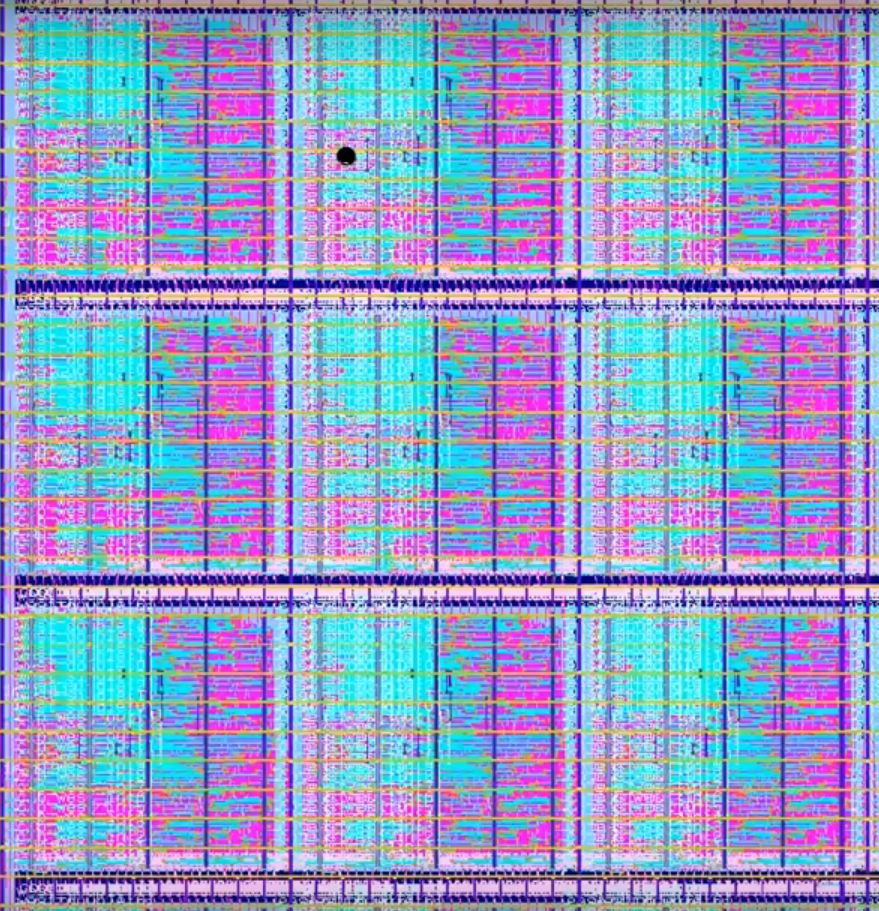

Looking inside an open source ASIC with Zeptobars

In this interview, I met up with Michael from Zeptobars in Zurich, Switzerland, where we use acid to decapsulate one of my Tiny Tapeout chips. This technique involves using acid to remove the protective epoxy layer of a chip, revealing the silicon die underneath. Decapping is commonly used to analyse the construction of integrated circuits. Michael usually decapsulates chips designed by others, sometimes decades ago, but this time one of the designs is his own.

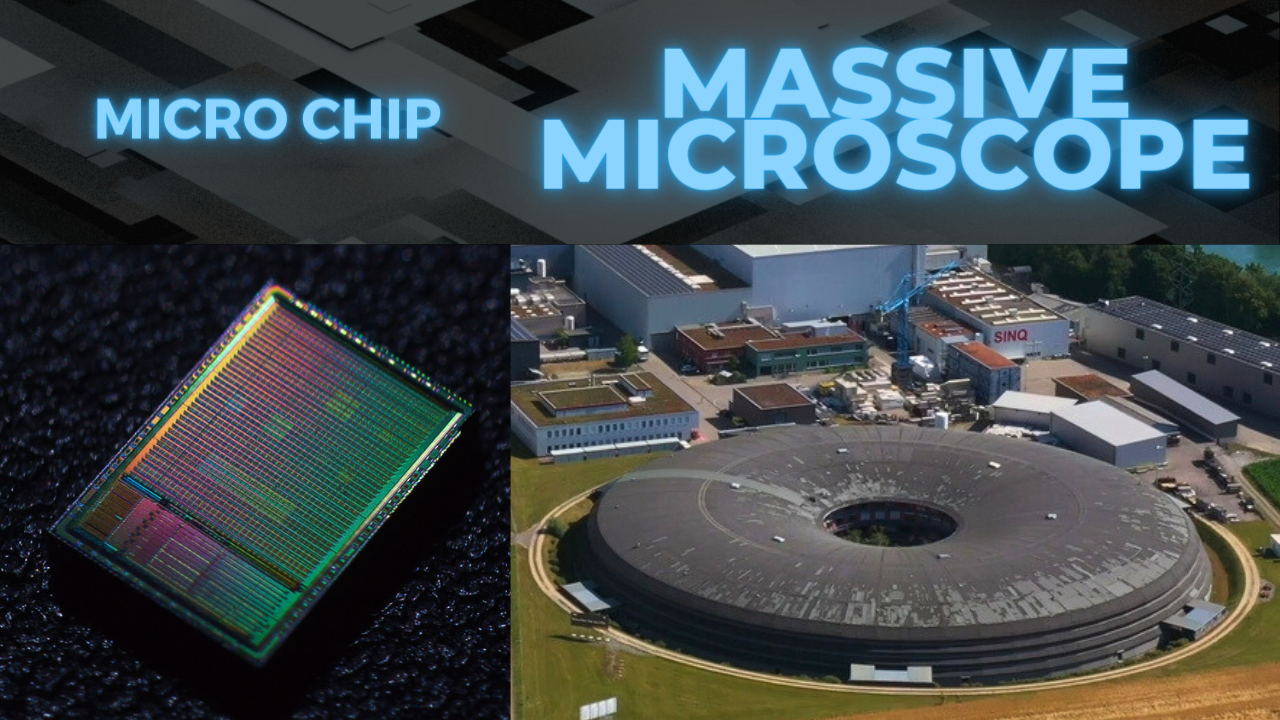

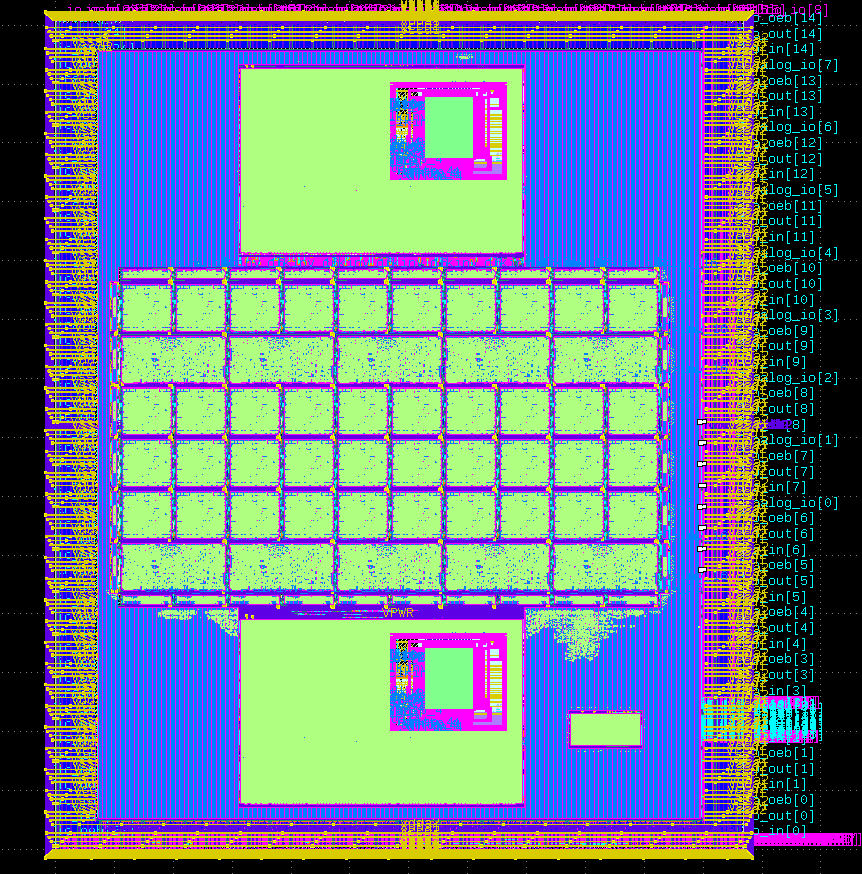

Looking inside my first ASIC with a particle accelerator

I got a once in a lifetime chance to use a particle accelerator to look inside my first ASIC!

It was amazing to be able to see all the different layers and match them up with the design files I sent to Efabless.

So join me on my journey to the Swiss Light Source at the Paul Scherrer Institut where I learnt how they use their synchrotron to make some awesome images!

I also have a public photo album if you want some SLS themed wallpaper!

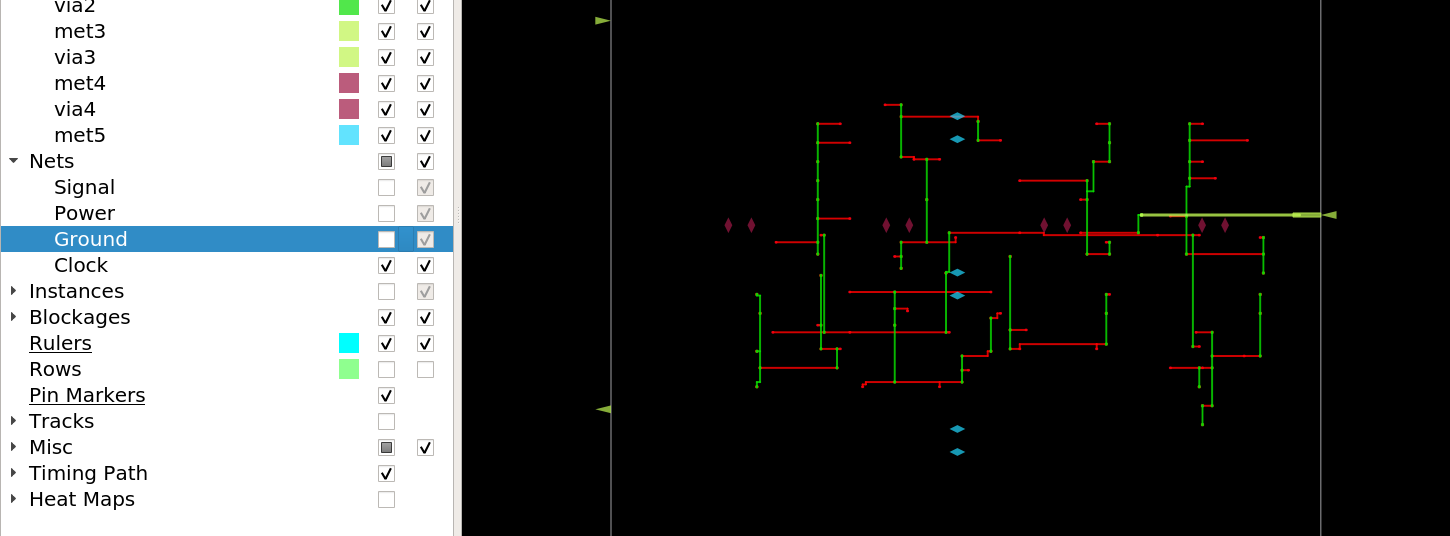

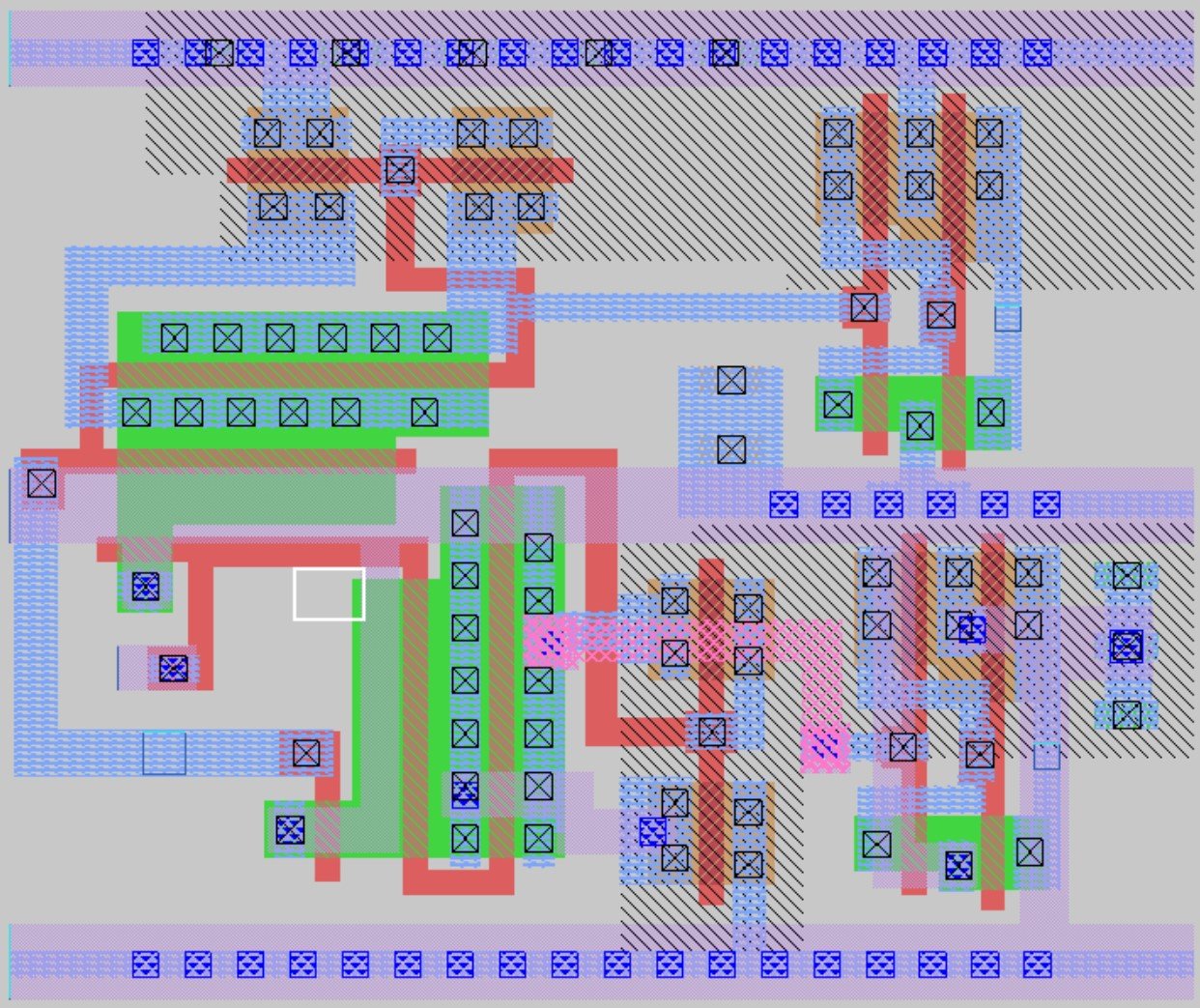

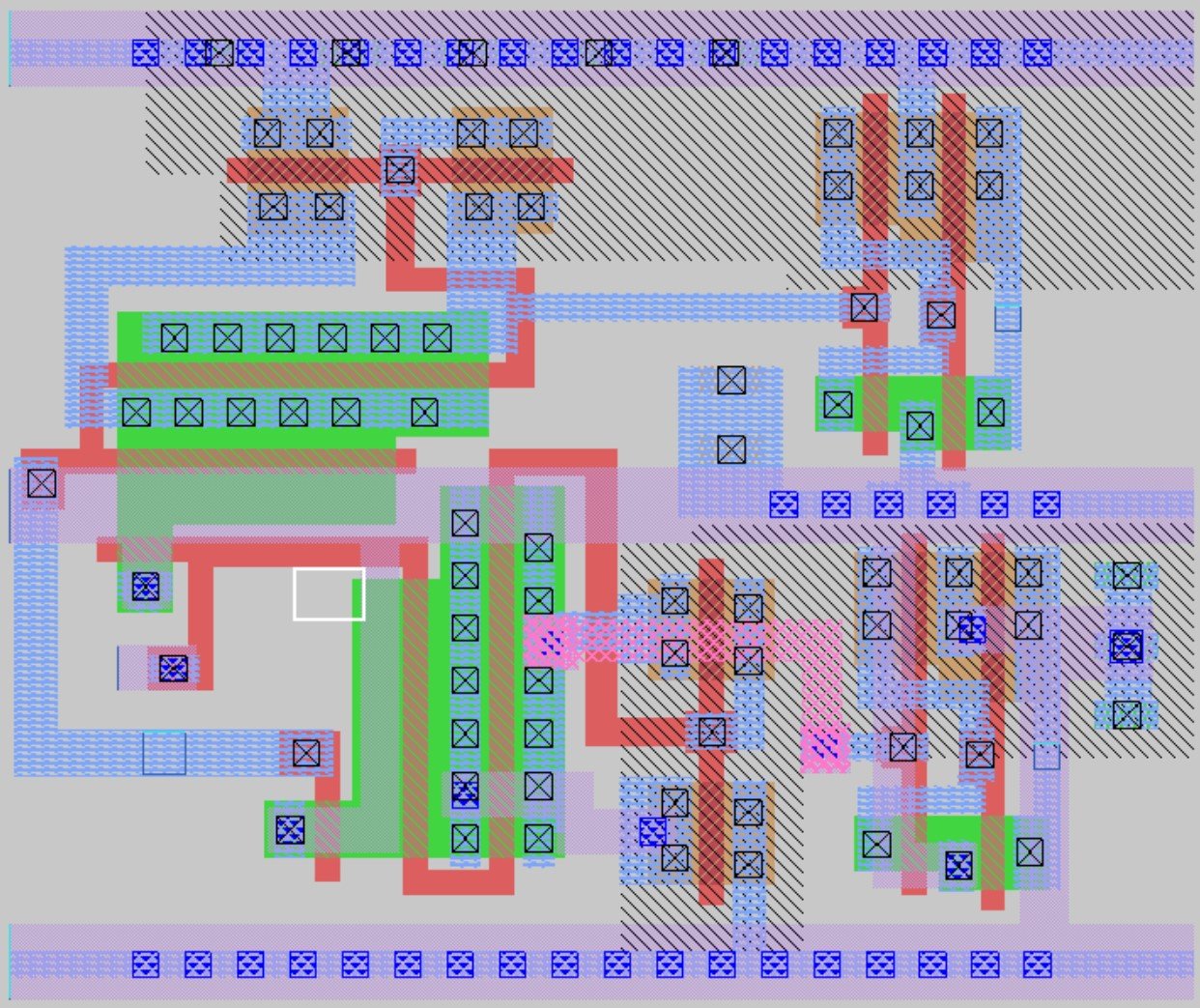

OpenROAD GUI

The OpenROAD GUI is a great way to explore your ASIC design. You can:

- View various types of heatmaps, including

- Placement density

- Power density

- Routing congestion

- IR drop

- Trace nets,

- View the clock tree,

- Inspect timing and more.

I recently spoke with Matt Liberty, and OpenROAD maintainer, and he showed me how to inspect a simple design.

OpenLane

If you’re using OpenLane to harden your ASIC designs, and you want to use the GUI, you might hit a segfault. If so, you’ll need to modify the OpenLane top level Makefile.

Interview With Tom Spyrou

Tom Spyrou is a long time EDA developer who has worked at large and small companies.

- In 1988 Developed QTV at VLSI technology. It was the first STA engine to be trusted to sign off devices for fabrication without timing based simulation.

- He was the original architect of PrimeTime STA algorithm.

- Manager of Cadence Common timing Engine and precursor to Open Access

- Senior technical positions at Synopsys, Cadence, Simplex, AMD, Altera and Intel.

Since 2019 he has been the Chief Architect and Technical Project Manager of OpenROAD since 2019.

Interview With Dirk Koch and Nguyen Dao

One of the popular types of entries to MPW1 & 2 have been FPGAs. I have previously spoken with Arya Reais-Parsi about their FPGA project submitted to MPW1.

In MPW2 I noticed there were a couple of applications that seemed fairly advanced - especially FuseRISC: 2 RISCV processors with embedded FPGA fabric between them.

Dirk & Nguyen kindly allowed me to interview them about:

- their FABulous eFPGA framework,

- support for Yosys & NextPNR,

- parameterisation of the fabric,

- blockrams with OpenRAM,

- their MPW applications and previous tape-outs, and

- their experience with the open source tools.

Enjoy!

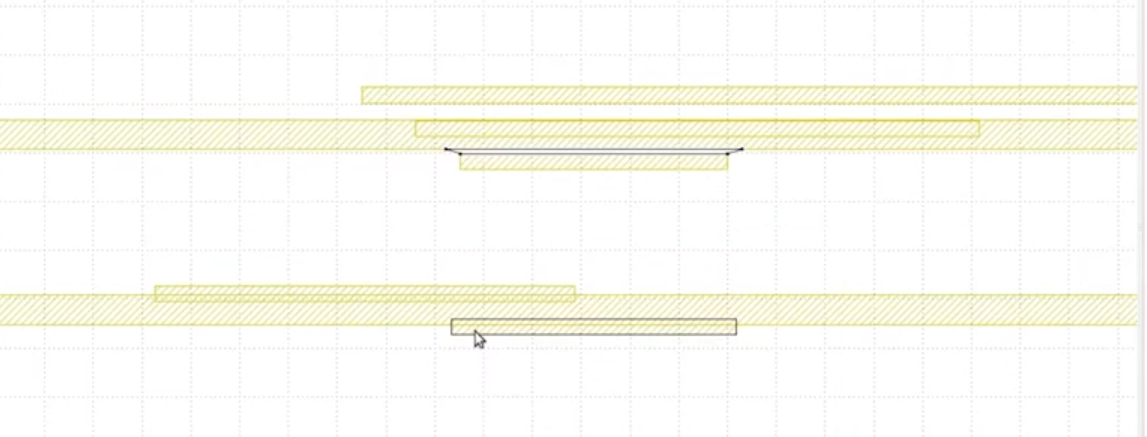

Last minute DRC fixes

The story of the first Open Source ASIC shuttle continues!

A few of the applicants to the first shuttle were recently contacted by efabless - they had discovered some DRC issues that couldn’t be waived by the foundry.

In my recent interview with Tim Edwards, he mentioned that Google are paying for a license of Calibre - another swiss army ASIC tool like Magic. This is to help make sure that the OpenLANE DRC hasn’t missed anything.

Interview with Tim Edwards - what happens between ASIC submission and sending to Skywater?

In this interview I talk with Tim Edwards from eFabless. He is their vice president of analog and platform.

We mostly talked about what needs to happen before they send the final files to Skywater.

A lot of the work is infrastructure:

- fetching files,

- compositing IDs,

- generating fill layers,

- a final DRC run.

Interview with Lakshmi S - PLL design

In this interview I talk with Lakshmi S about their shuttle submission.

As well as convering what a PLL is and its component parts, we also answered some interesting questions from the twitter community:

- how long things take to design, what is fun and what is frustrating,

- how to change the PLL’s response,

- why design a integrated loop filter,

- process corners and ngspice

- post silicon testing.

The repository is here.

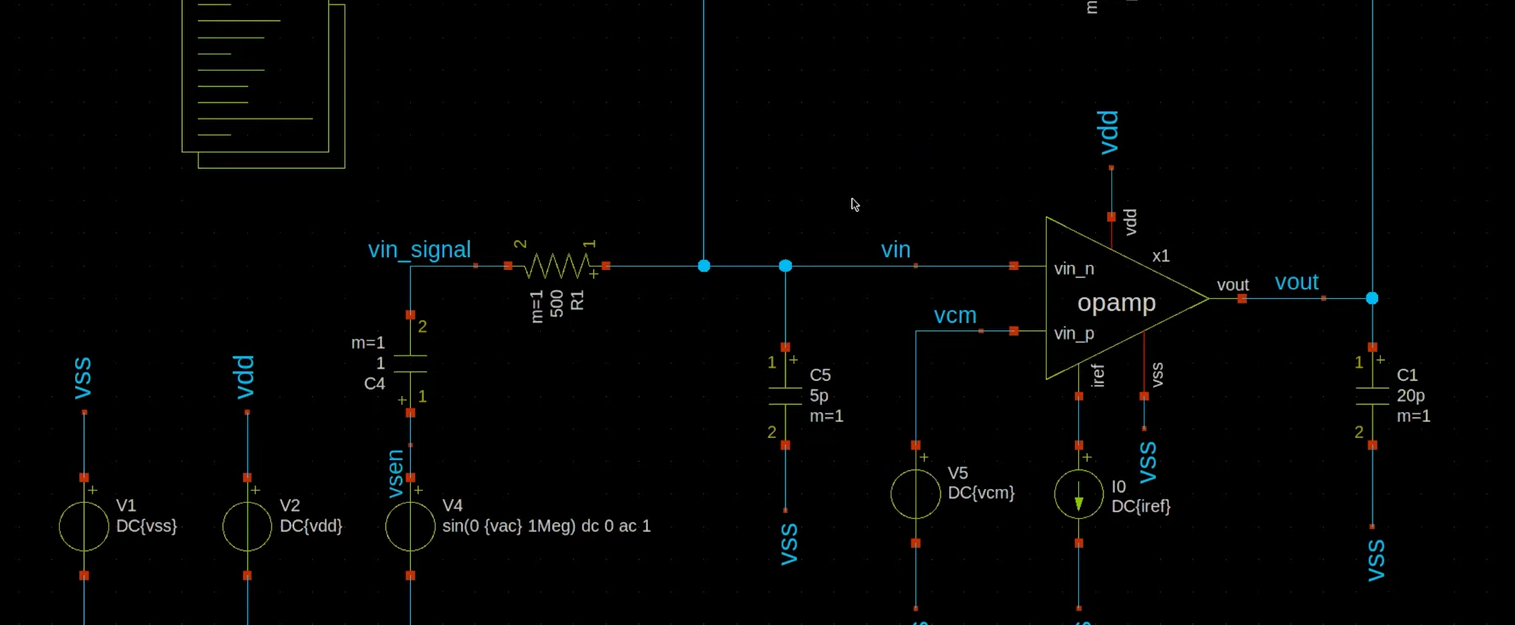

Interview With Diego Hernando

In this interview I talk with Diego Hernando about their ASIC submission.

They have been working on some analog blocks; mostly op-amps but also including a PLL from another designer.

We discuss the difference between digital and analog design, the tools, simulation, layout and testing.

Here’s the link to the repository

Interview with Arya Reais-Parsi - FPGA fabric

In this interview I talk with Arya Reais-Parsi about their shuttle submission. They are working with a group of students to create Open Source FPGA fabric that can be put on an ASIC and configured with yosys/nextpnr.

The repository is here.

Interview With Sylvain 'tnt' Munaut: USB peripherals

In this interview I talk with Sylvain ’tnt’ Munaut about his Google/Skywater ASIC application.

The design is especially interesting to me because of the way it merges the SRAM blocks with the logic. This has been a major challenge in my own design.

Here’s the link to the repository

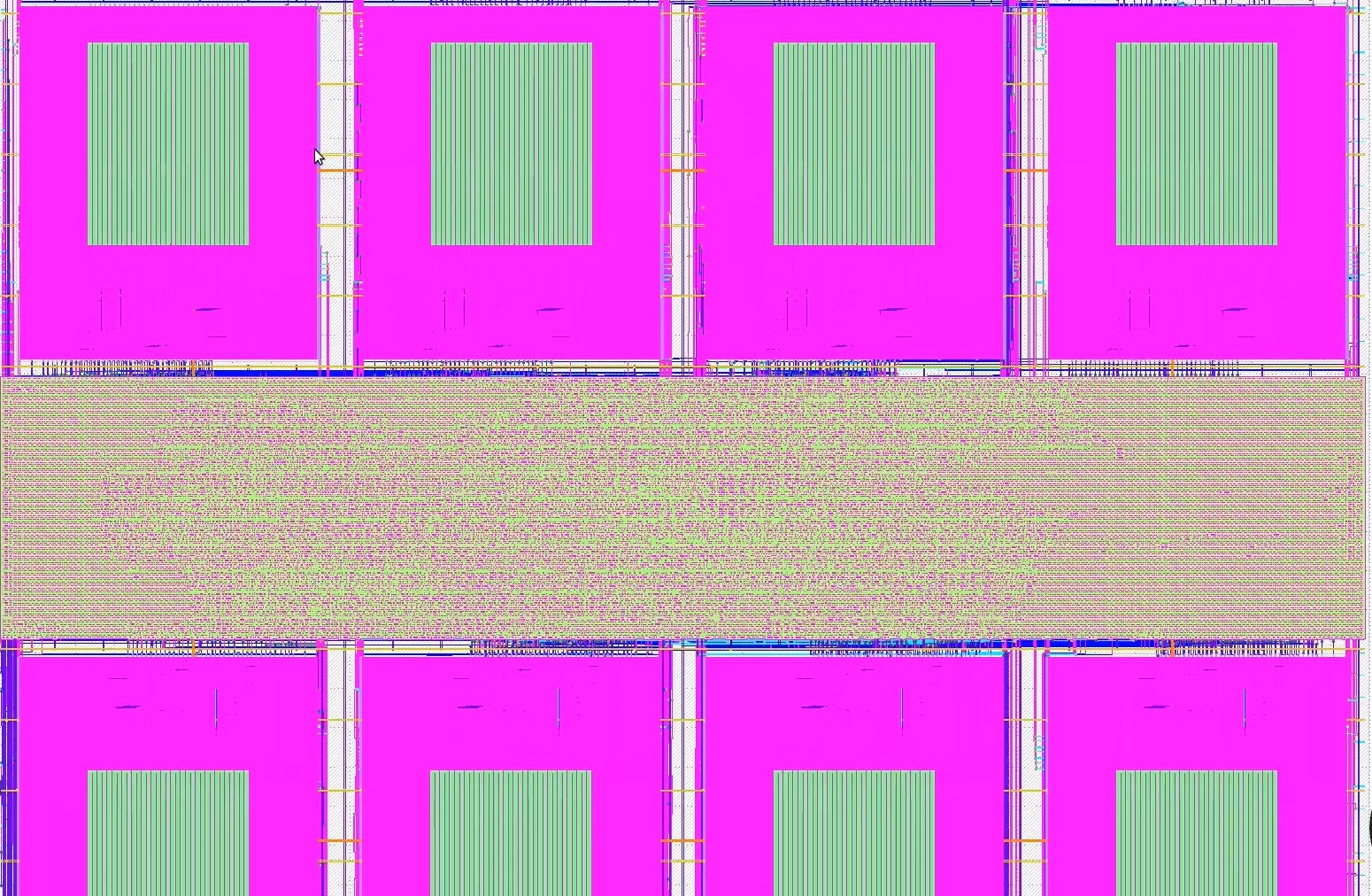

Interview With Vladimir Milovanović - spectrometer with Chisel

In this interview I talk with Vladimir Milovanović about putting a spectrometer on the Google/Skywater/Efabless ASIC shuttle.

He created the design using Chisel.

The repository is here.

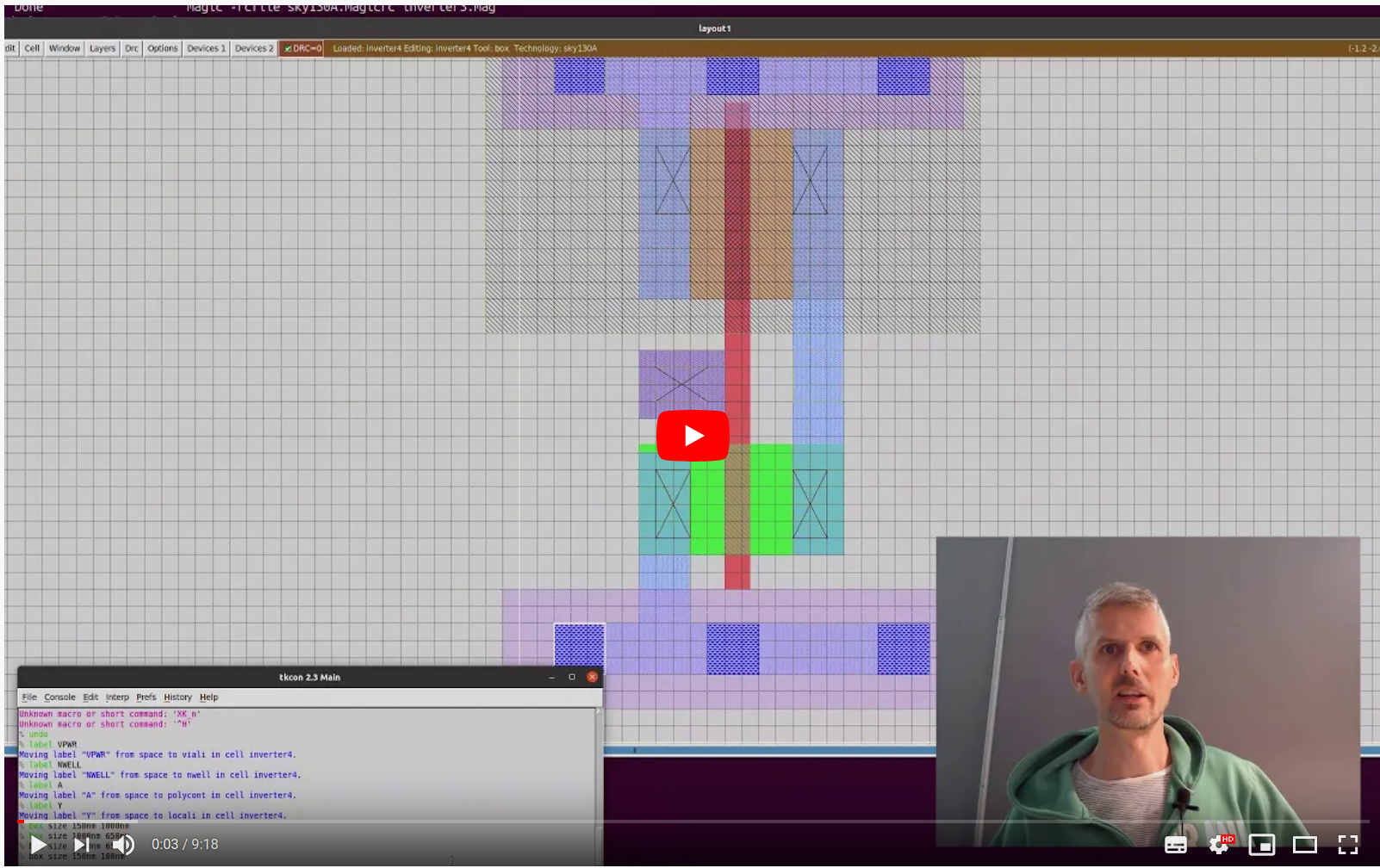

Inverter

A standard cell is a building block that contains some basic digital or analogue functionality. These blocks are then tiled together to make the final design.

Since finding out about the Skywater PDK, I wanted to try drawing my own ‘standard cell’ using the Skywater transistor models.

An inverter is one of the simplest and even that was quite difficult! As you can see below it contains an N and P type MOSFET.