Short articles about my experience with making ASICs, interviews and any other related topics I think are interesting.

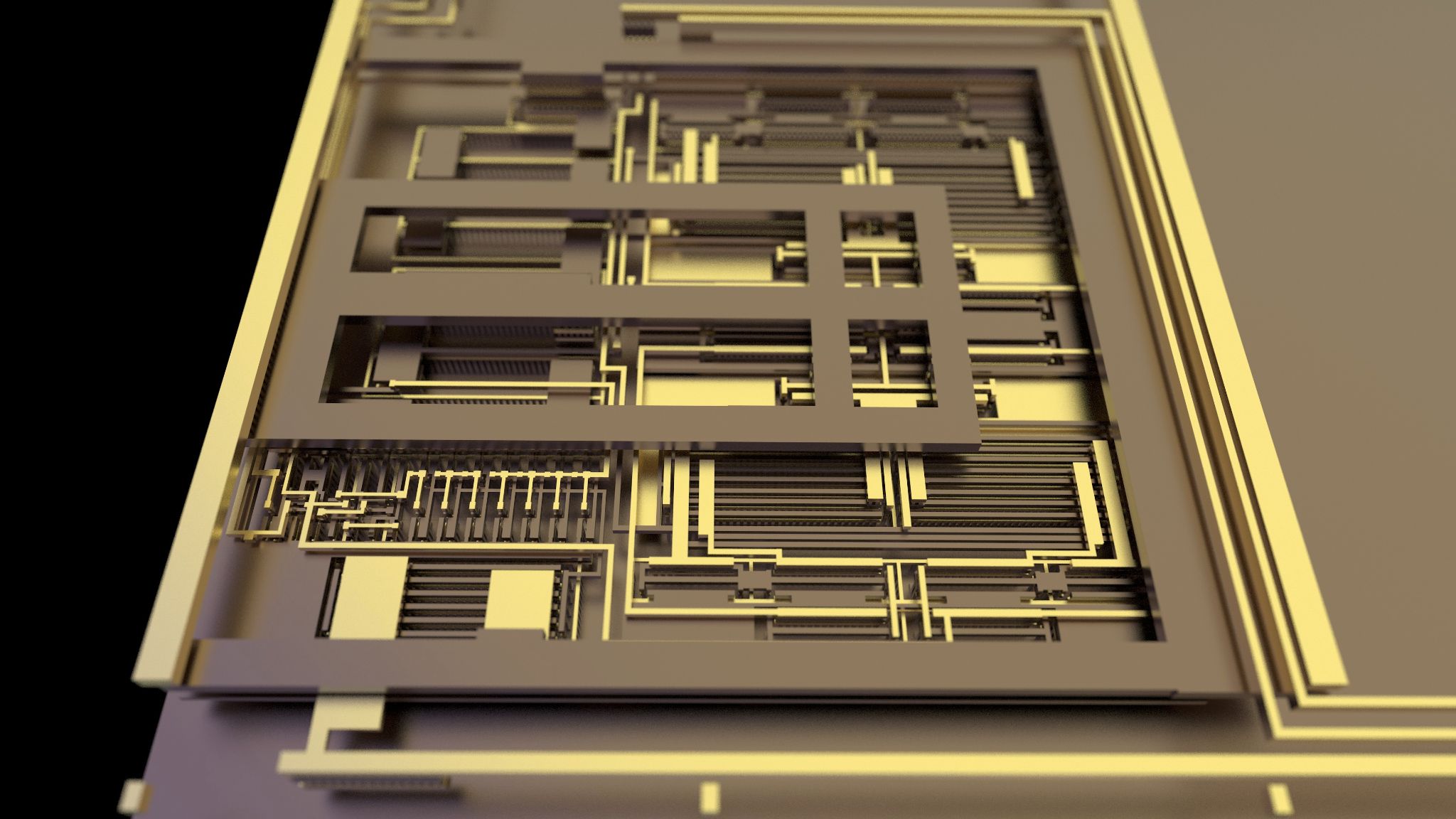

Tiny Tapeout 9

Tiny Tapeout 9 closed with 95% utilisation! It was our best ever run, with 369 designs submitted from 21 countries.

Among the digital projects we had an Atari 2600 (with games), a wide range of CPUs and even some SDR projects.

On the analog side we had PLLs, opamps, ADCs, DACs and time to digital converters.

For all the projects, check the chip’s page.

I printed the datasheet, and it’s hefty! Download it here.

Get started with open source ASICs

In my recent video Getting started with open source ASICs, I provided an overview of the open-source silicon movement, highlighting key resources and tools while showcasing some inspiring projects.

The video starts by looking back at the game-changing moment in 2020 when Google, Tim Ansell, and Efabless announced their free shuttle program, making it possible for anyone to get their open-source chip designs manufactured. This sparked a wave of innovation, with many taking their first steps in ASIC design using open-source tools like OpenLane and the Skywater 130nm PDK.

My analog microelectronics journey

This article will give you some insight into my journey into the world of analog microelectronics, as told in my recent talk at ORConf 2024.

Back in 2020, inspired by Tim Ansell’s announcement of free tapeouts, I jumped headfirst into the world of open-source ASIC design. My first chip was a digitally focused project, reflecting my background in FPGA programming. It was amazing to see the power of digital abstraction—designing with ones and zeros, instantiating tons of transistors with a single line of code—but it also made me appreciate the incredible complexity hidden beneath the surface.

Looking inside an open source ASIC with Zeptobars

In this interview, I met up with Michael from Zeptobars in Zurich, Switzerland, where we use acid to decapsulate one of my Tiny Tapeout chips. This technique involves using acid to remove the protective epoxy layer of a chip, revealing the silicon die underneath. Decapping is commonly used to analyse the construction of integrated circuits. Michael usually decapsulates chips designed by others, sometimes decades ago, but this time one of the designs is his own.

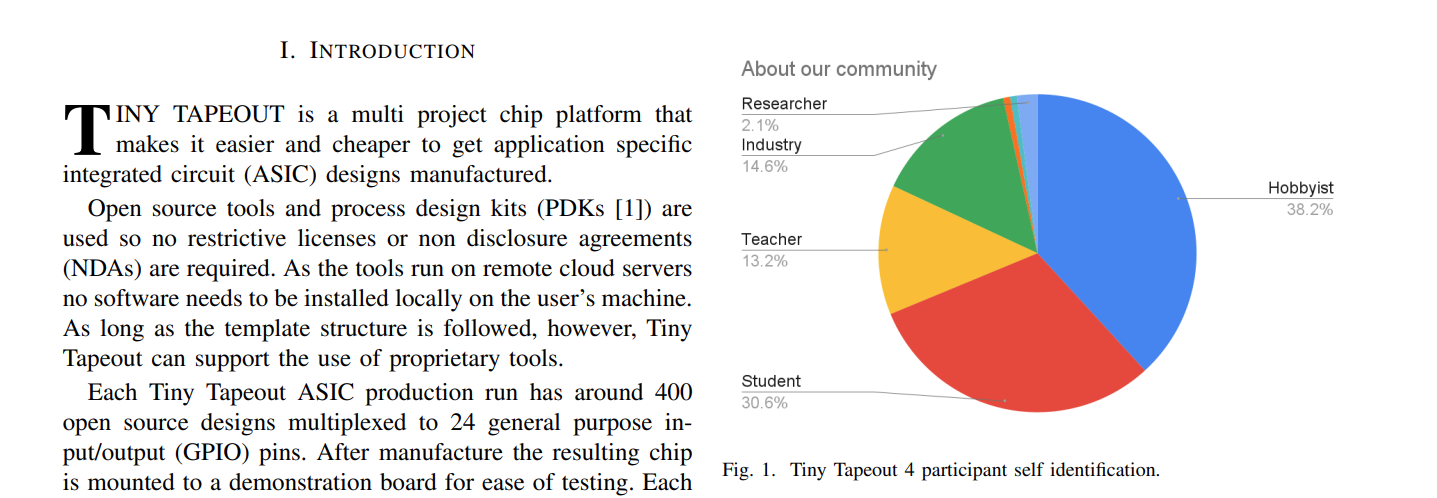

Tiny Tapeout IEEE paper

I’m very happy to announce that my paper about Tiny Tapeout has just been published by the IEEE solid state circuits magazine!

Tiny Tapeout aims to make it easier and cheaper than ever to design and manufacture custom Application-Specific Integrated Circuits (ASICs). I originally conceived of the idea in September 2022 as a way to guarantee silicon for my course participants.

If you’re an IEEE member, you can read it here: https://ieeexplore.ieee.org/document/10584359, otherwise you can read the preprint: https://www.techrxiv.org/users/799365/articles/1165896-tiny-tapeout-a-shared-silicon-tapeout-platform-accessible-to-everyone

Tiny Tapeout Goes Analog!

Tiny Tapeout 6 marked a significant milestone by introducing support for analog and mixed-signal ASIC designs. This innovation opened up a world of possibilities for open-source chip development, building on the project’s success in the digital realm.

Prior to Tiny Tapeout 6, only digital designs were supported. However, the demand for analog and mixed-signal capabilities was evident. In an interview, Carsten Wulff, Principal IC Scientist at Nordic Semiconductor, expressed his enthusiasm for the open-source ASIC movement, noting that a key strength of this approach lies in the mixed-signal domain. FPGAs and microcontrollers excel in digital applications, but mixed-signal designs on ASICs offer unique advantages and capabilities.

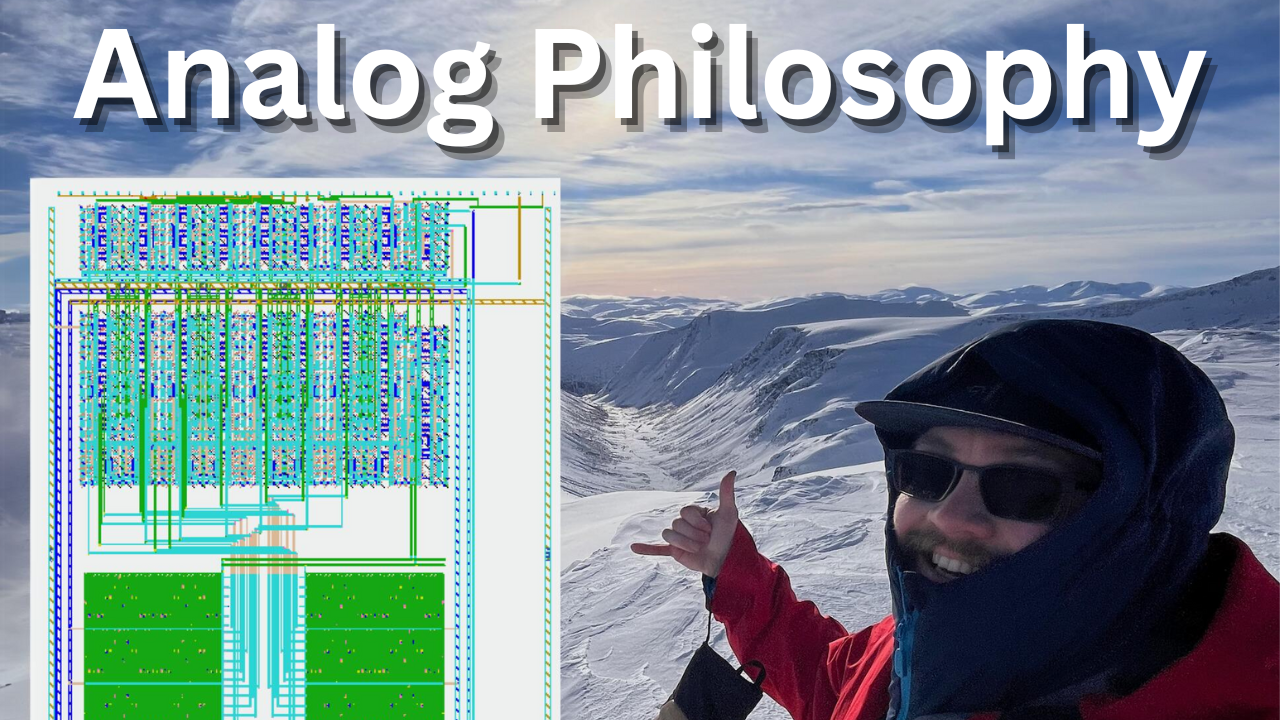

Analog Philosophy with Carsten Wulff

In this insightful interview, I talk with Carsten Wulff, Principal IC Scientist at Nordic Semiconductor, about all things analog ASIC design.

Carsten kicks things off by sharing a fascinating anecdote about how he ended up designing an analog SAR during his winter holiday in the Norwegian mountains, sparked by the opportunity to include analog designs on Tiny Tapeout 6.

The conversation then shifts to Carsten’s thoughts on the accessibility of 130nm technology for analog design, which he believes is “the last comfortable node”. While larger designs with millions of digital gates might not be suitable, 130nm shines for analog applications, offering a sweet spot between performance and cost-effectiveness.

Review of 2023 and aims for 2024

Hi and happy new year! Welcome to my year in review post of 2023. We’ll revisit the biggest moments of open source semiconductors, the goals I failed and those I met, and set some new ones for 2024!

So, let’s start with the biggest news of 2023.

Last year saw the end of the Google sponsored lottery shuttles. We were expecting around another 8 shuttles for sky130, GF180 and the start of sky90. The last shuttle was GFMPW1, which closed late last year and the Sky 130 PDK is now in the safe hands of the chips alliance.

VGA clock PCB updated for new chips

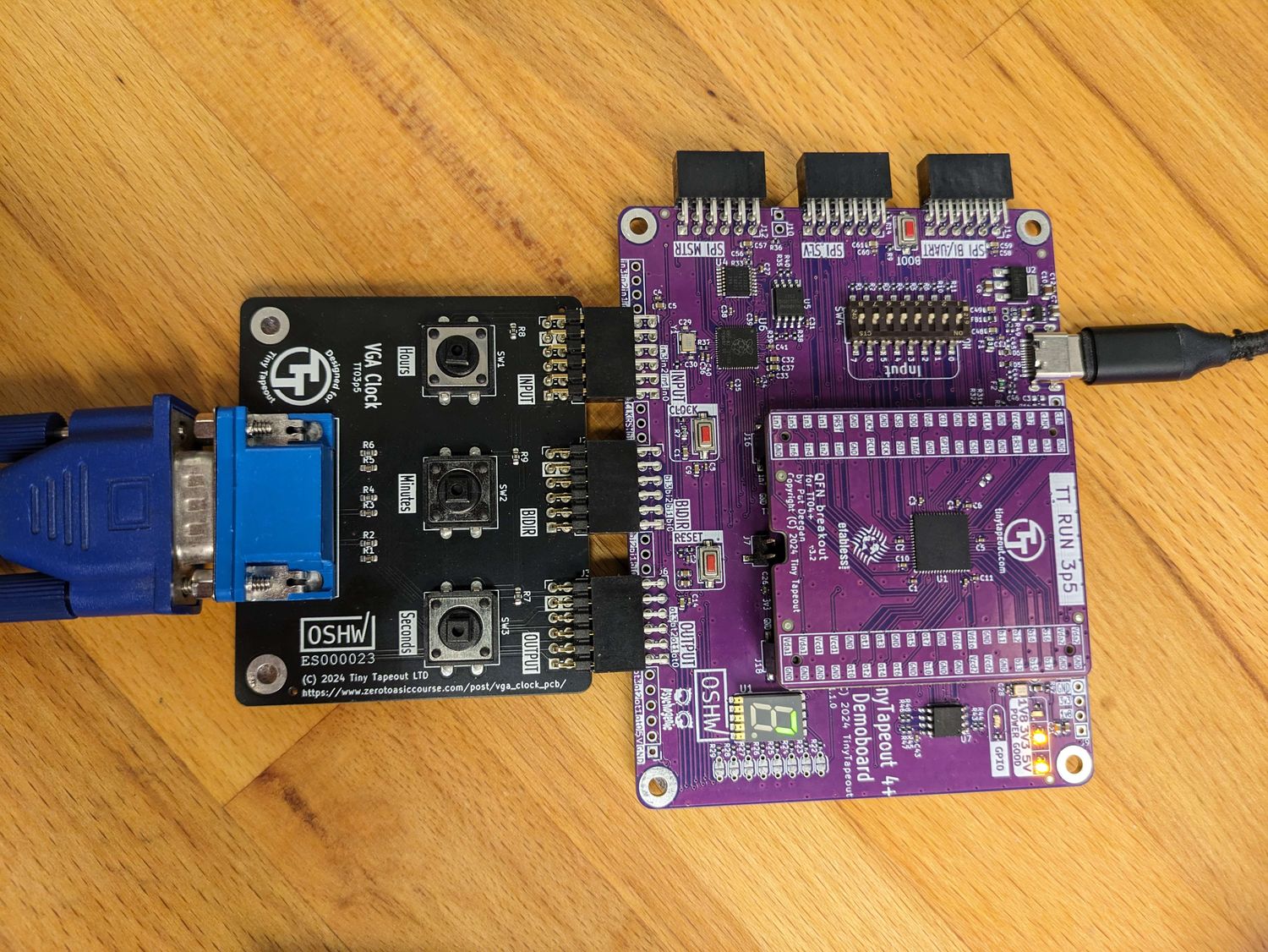

My VGA clock design is the world’s first certified open source hardware down to the chip level.

Unfortunately the MPW1 chips were very hard to use and the new ones have a different pinout and footprint. I’ve been using the clock design as a test project for all the Tiny Tapeout chips past TT03.

To test the new mux structure introduced at TT04, we ran an experimental TT3.5 chip. The chips are back and the clock works as expected (phew!)

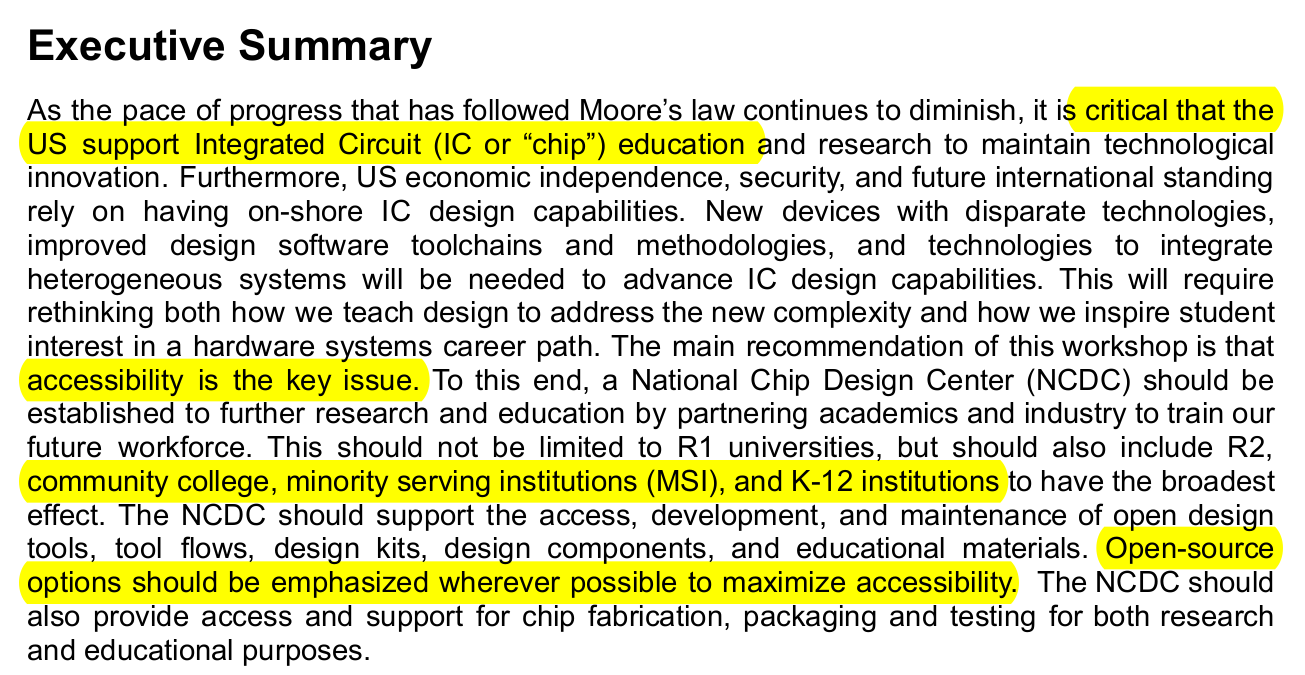

NSF Report recommends open source for accessibility

The EU and US have pledged $100B investment in semiconductors with their chips acts. A huge percentage will go to building new fabs, but both acts acknowledge that factories are no use without trained people to run them.

The NSF commissioned a report on research, education and workforce development - recently delivered by Matthew Guthaus, Christopher Batten, Erik Brunvand, Pierre-Emmanuel Gaillardon, David Harris, Rajit Manohar, Pinaki Mazumder, Larry Pileggi & James Stine.