Netlist

A netlist is a machine readable file that contains all the connections between all the components in your design.

They are one of the outputs of a Synthesis tool like Yosys.

These examples are taken from http://bygone.clairexen.net/yosys/screenshots.html

If you have a counter design written in an HDL like Verilog

module counter (clk, rst, en, count);

input clk, rst, en;

output reg [3:0] count;

always @(posedge clk)

if (rst)

count <= 4'd0;

else if (en)

count <= count + 4'd1;

endmodule

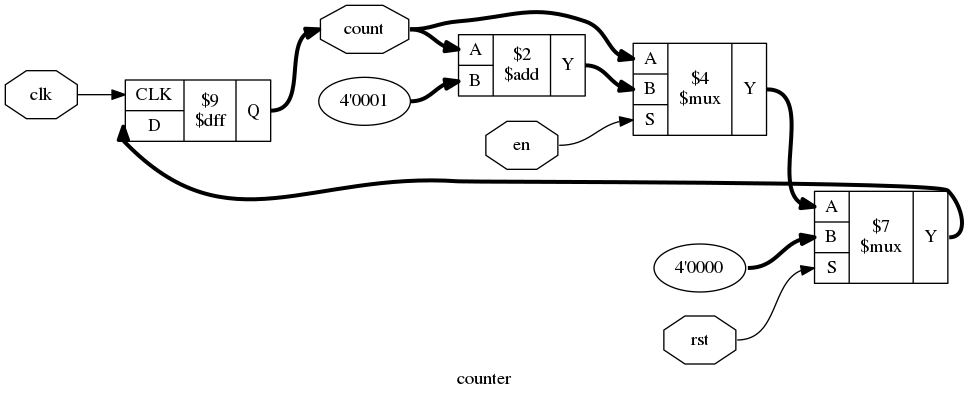

The output netlist can be visualised like this:

You can see the blocks are fairly ‘high level’, like multiplexors ($mux), or adders ($add). These types of blocks are not part of the Skywater PDK, so they need to be broken down into more simple blocks.

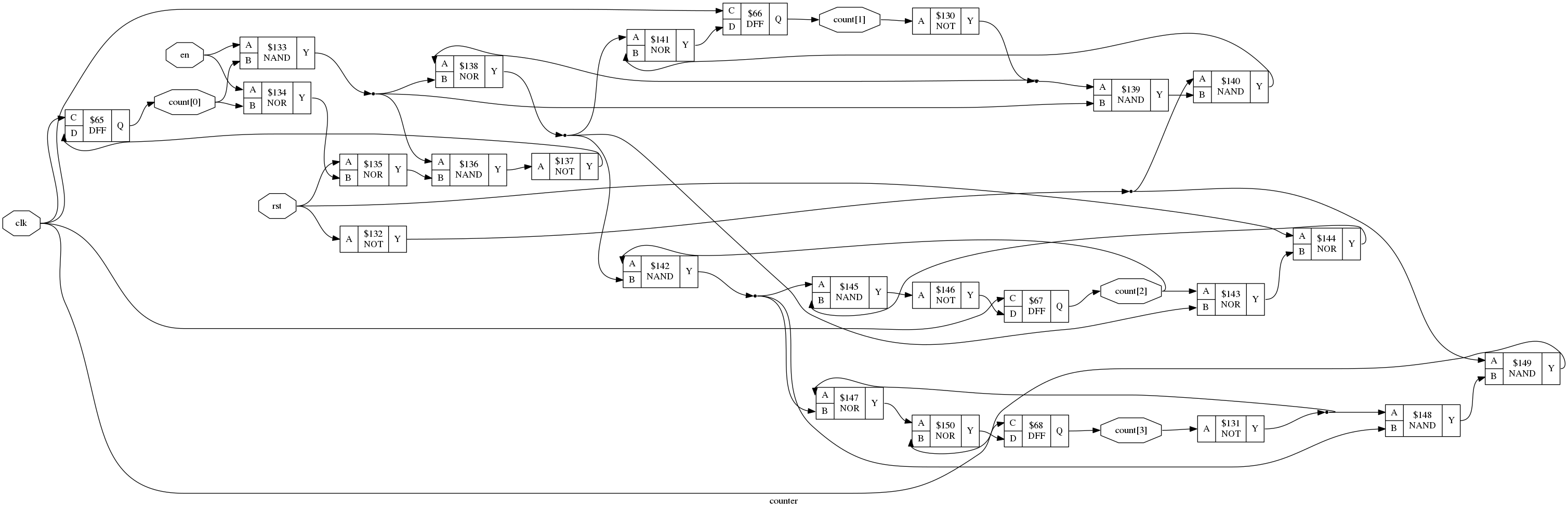

These blocks are now simple enough that they can be mapped onto the standard cells we have in the PDK. The synthesis process is the first step in the LibreLane tool.

Course feedback

This is the most comprehensive IC design course on the internet. I loved working on my mixer module and Matt's team helped every time I got stuck. I will do further tapeouts for sure.

Kolos (analog course)