PDN

The Power Delivery Network is what provides power for all the macros in your design.

For the shuttle, LibreLane creates a PDN that supplies the 4 rails available to the user project area:

inout vdda1, // User area 1 3.3V supply

inout vdda2, // User area 2 3.3V supply

inout vssa1, // User area 1 analog ground

inout vssa2, // User area 2 analog ground

inout vccd1, // User area 1 1.8V supply

inout vccd2, // User area 2 1.8v supply

inout vssd1, // User area 1 digital ground

inout vssd2, // User area 2 digital ground

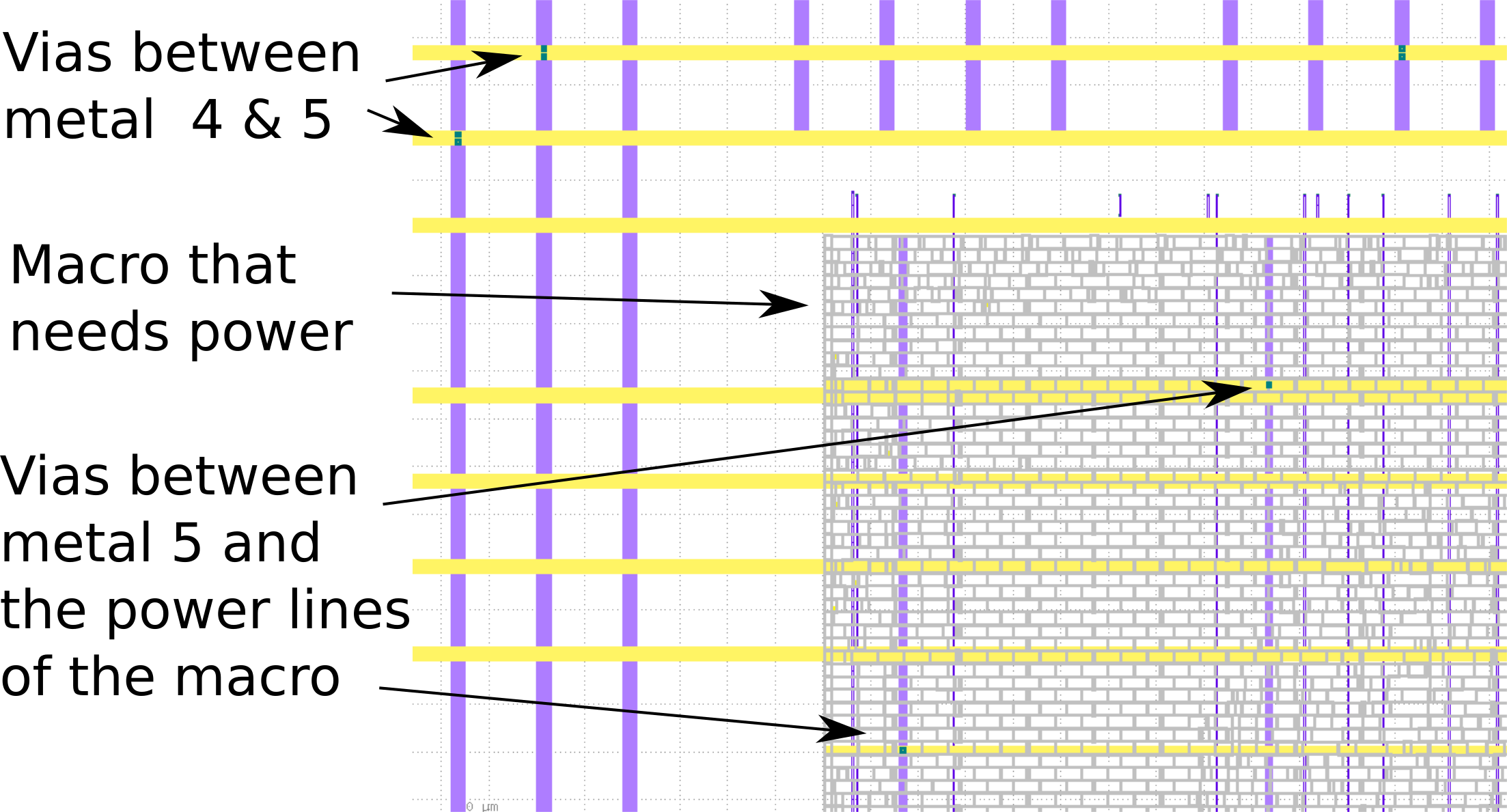

Metal 4 is used for vertical lines that are cut for the macros, and Metal 5 routes over the top of everything. When the metal 5 lines pass over the macro, vias are dropped to connect the macro’s internal PDN to the user project area’s PDN.

A common failure for small designs with the LibreLane tools is that there isn’t enough area for the PDN to get created. A simple fix is setting the absolute size of the die to make sure its large enough.

Course feedback

At first I wasn’t interested in testing at all, but by the end of the course somehow it got quite fascinating just to figure out all the ways to test the design.

Renaldas Zioma (digital course)