Short articles about my experience with making ASICs, interviews and any other related topics I think are interesting.

MPW7 submitted!

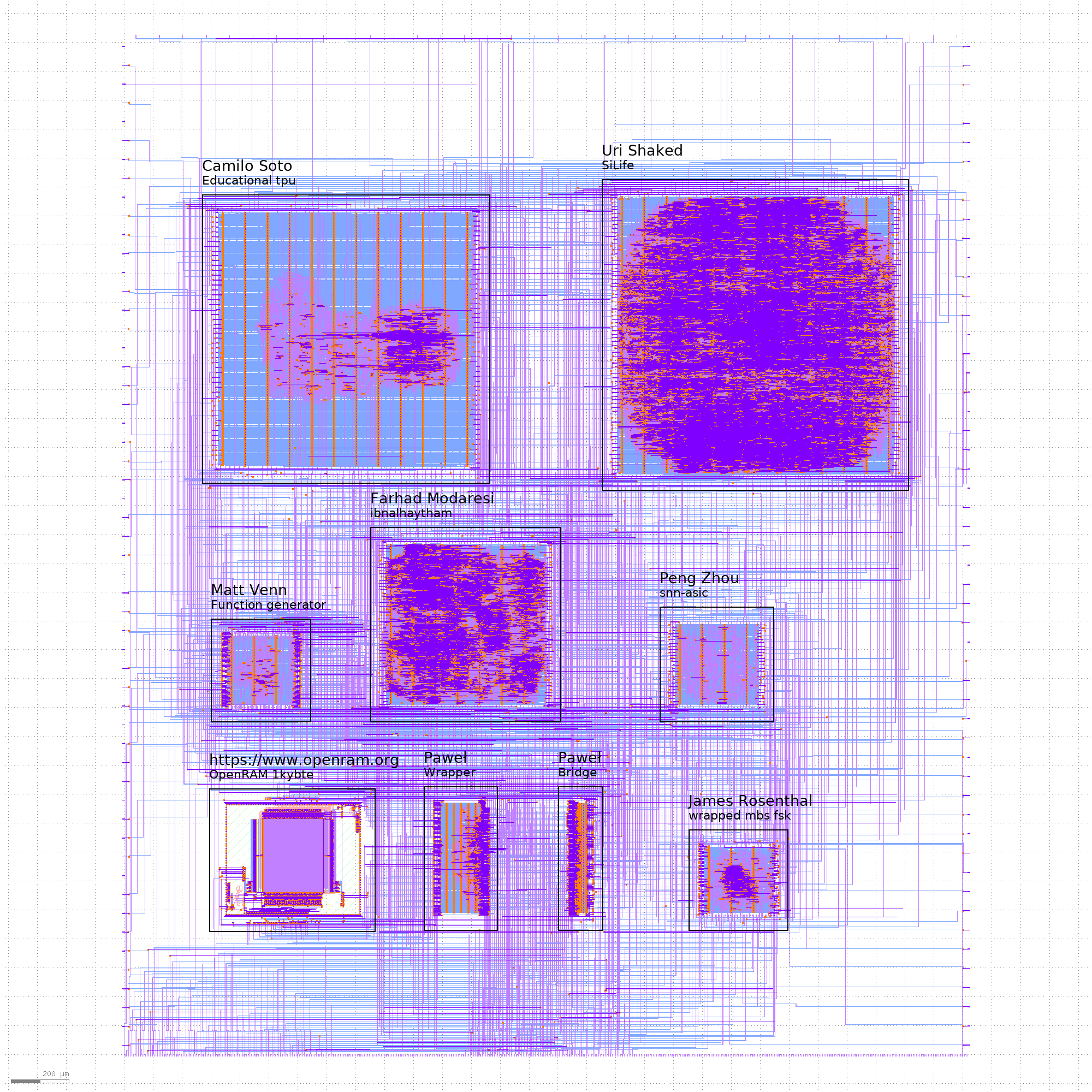

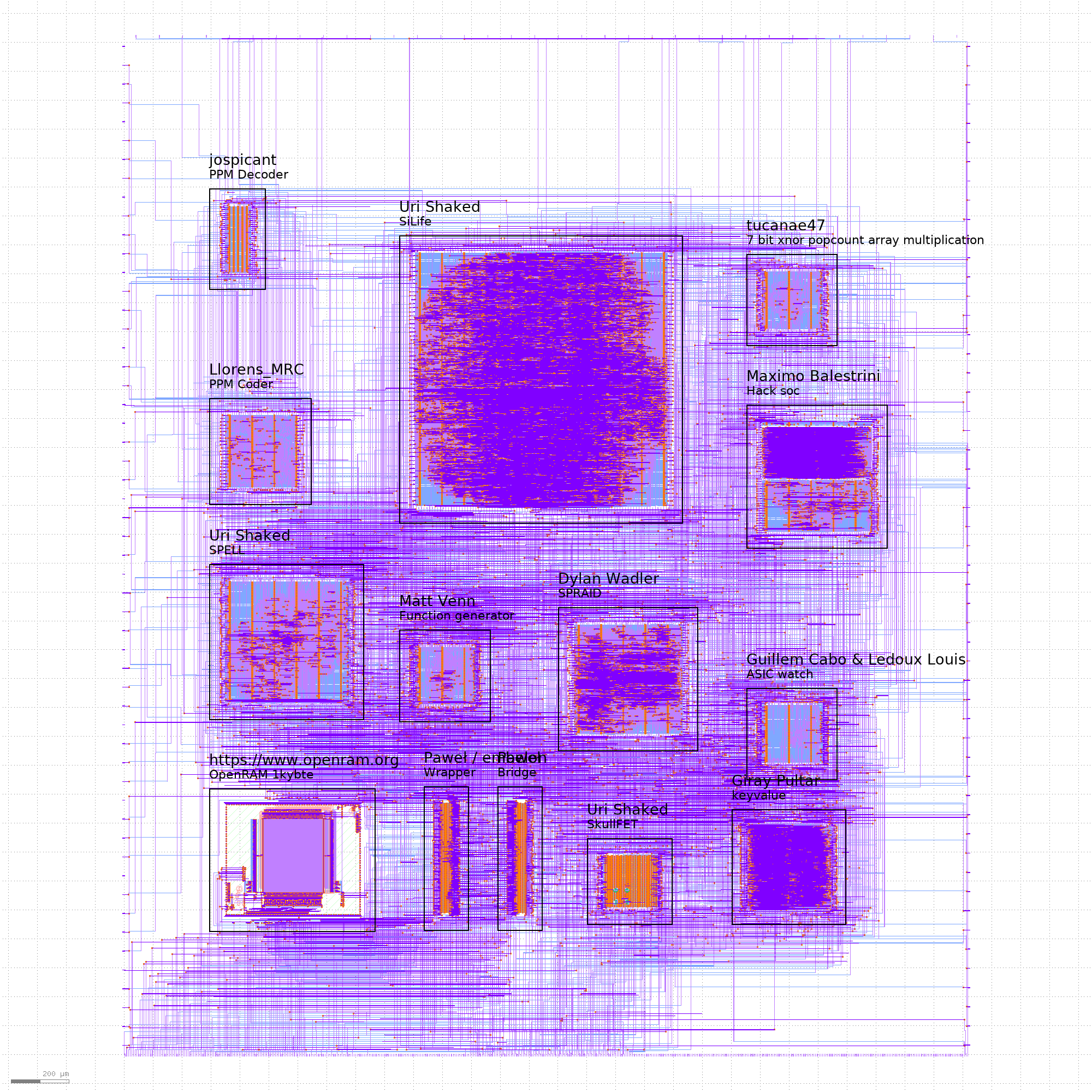

We submitted for MPW7! I am particularly excited about this submission because we were able to submit the Zero to ASIC course designs as well as the first Tiny Tapeout design.

MPW7 has by far had the most submissions of the MPW shuttles so far with 72 submitted projects as of 13 September.

Congratulations to everyone on the course submission! We had 9 projects from the course, with 1 demo arbitrary function generator from me, a 32-bit RISC-V based processor by Farhad, an in silicon version of Conway’s Game of Life from Uri and a Spiking Neural Network (SNN) accelerator by Peng Zhou. We also implemented 1kByte of RAM with open-source OpenRAM.

Instrumenting Hardware Adders

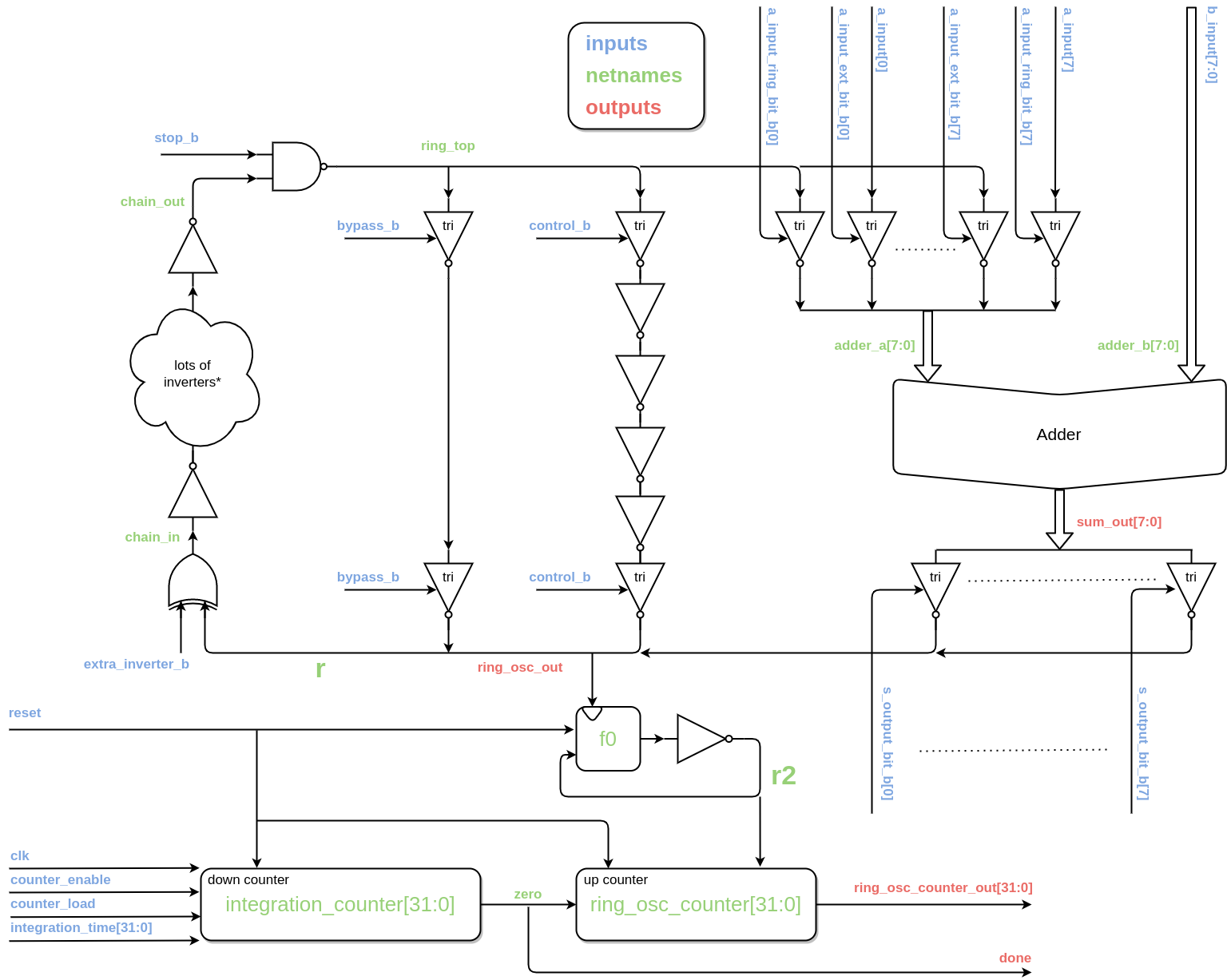

Following my interview with Teo on optimising hardware adders, I thought it would be a great project to tapeout on MPW6.

I wrote about the process on twitter:

I'm working on putting @td_ene 's adder work onto MPW6. Work in progress repo here: https://t.co/OBg8jQG1HJ

It was very easy to generate the adders, but I'm getting stuck on instrumenting them. I need to measure the performance inside the chip to get accurate results. pic.twitter.com/3CJvjmNzGI

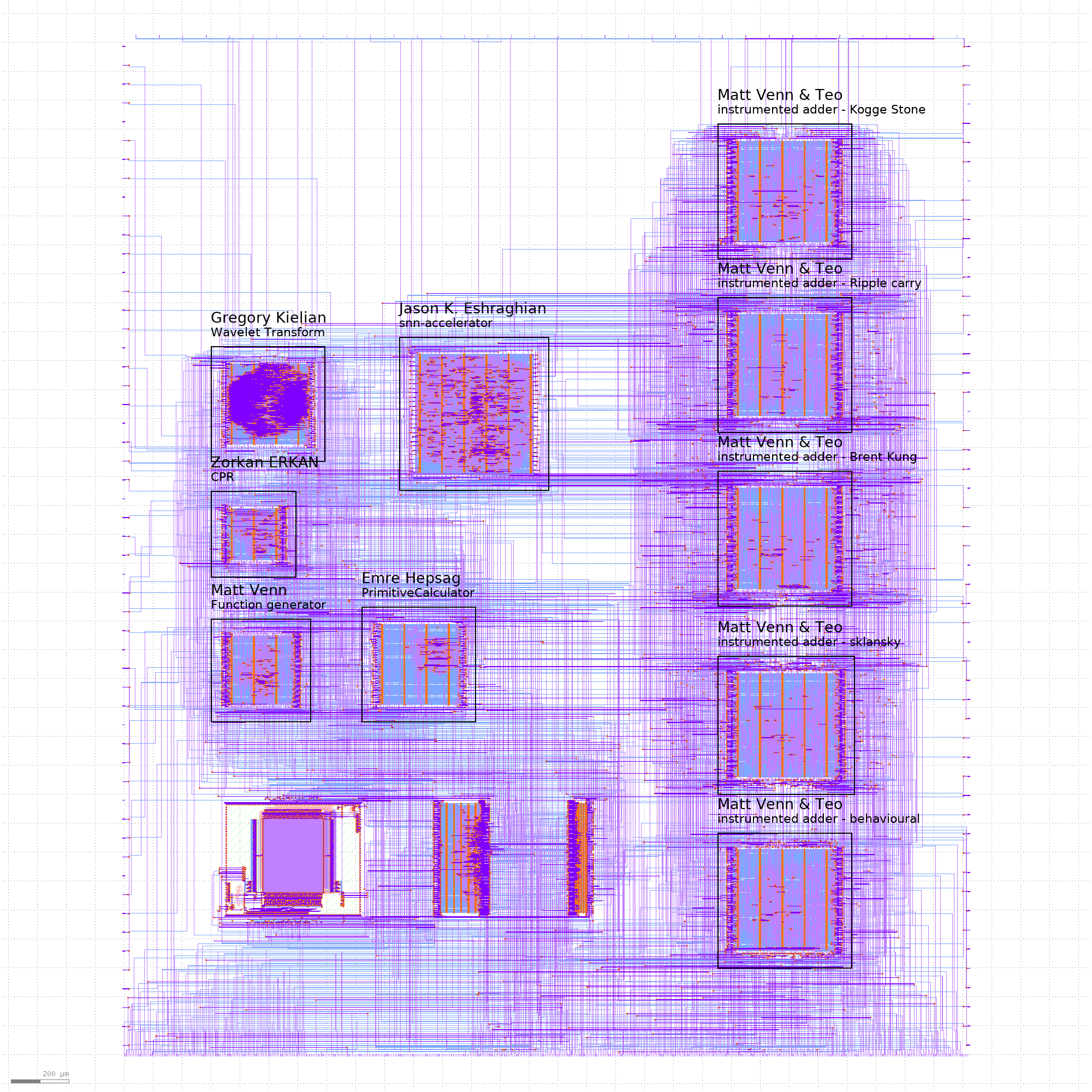

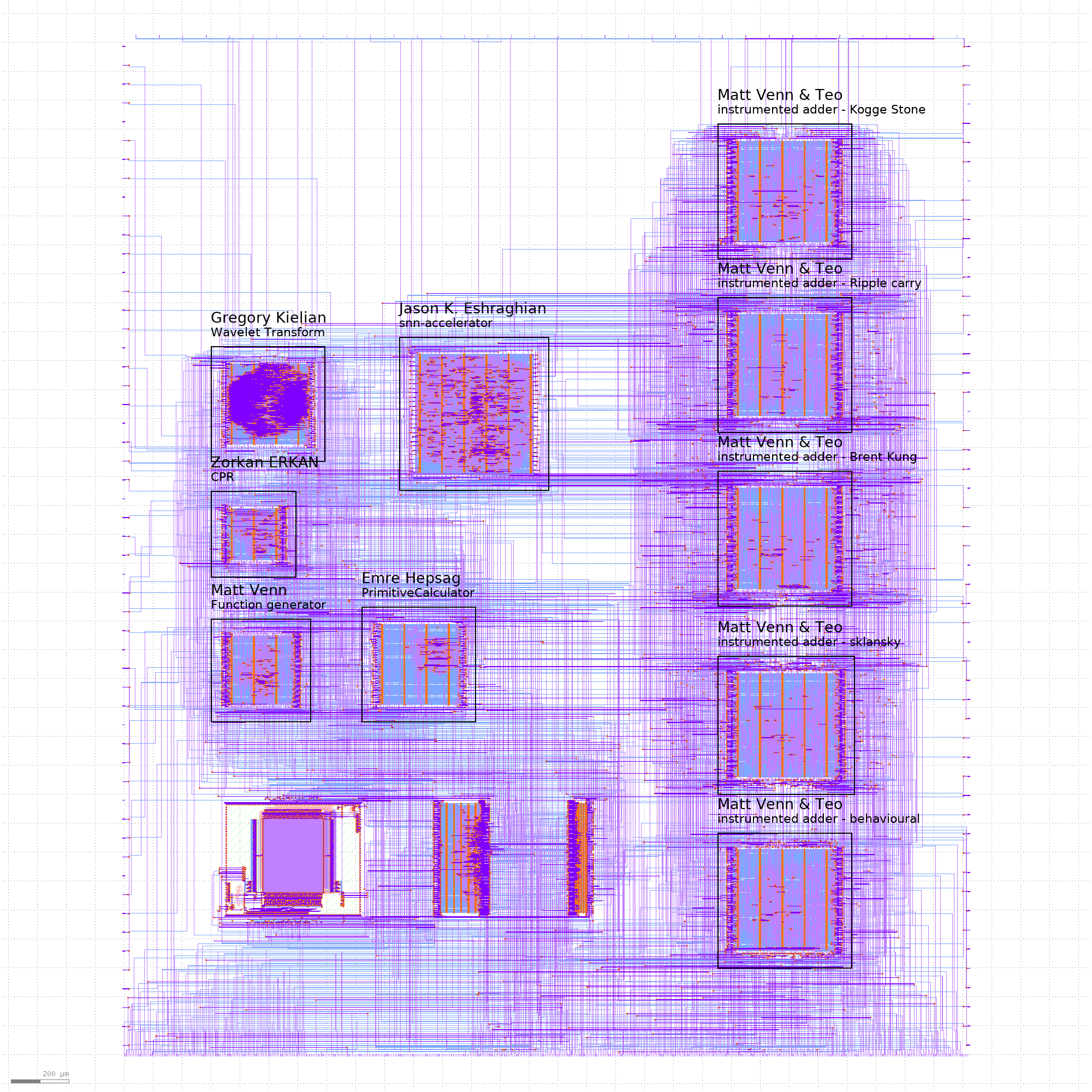

MPW6 submitted!

We submitted for MPW6!

We had 4 submissions from the course, the shared SRAM infrastructure, and I did some work on instrumenting Teo’s hardware adders.

Congratulations to:

- Zorkan ERKAN

- Emre Hepsag

- Gregory Kielian

- Jason K. Eshraghian

for getting your first ASIC designs on the submission!

We also had some people from the course make personal applications for a whole chip:

- Shumpei Kawasaki - MARMOT SOC

- Maximo - Hardware implementation of the Hack Computer from the Nand to Tetris courses,

- Proppy - HSV Mixer

Here’s the github repo for the group submission and the Efabless project.

ASIC Development in the Cloud

Proppy has been doing some great work with preparing the open source ASIC tools to work inside Jupyter notebooks. This means that you can now experiment with simulation and ASIC hardening without needing to download or configure the tools.

I think this is going to be of great importance for academia and education:

- Now when people publish papers they can include a link to a notebook that reproduces the published results.

- For education, it’s going to be so much easier to do a class workshop without having to install tools or maintain VMs.

Proppy demonstrated and explained his work in this interview.

Interview With Teo

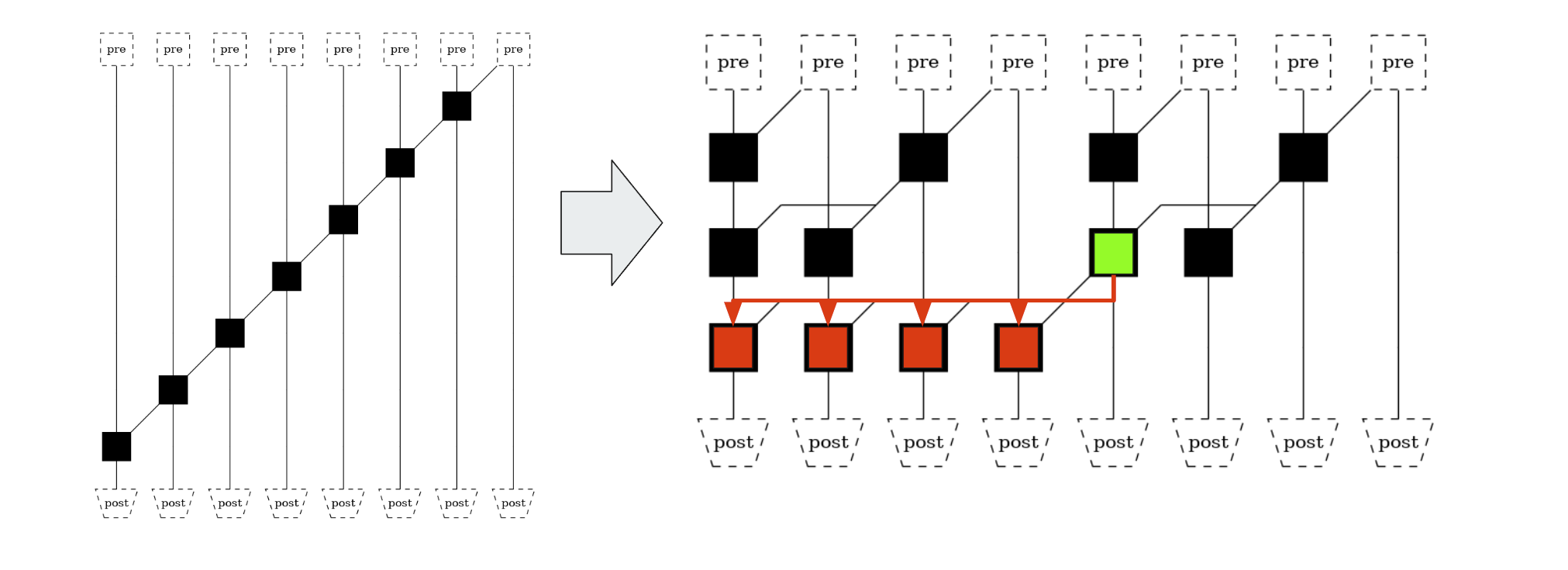

Teodor-Dumitru Ene has been doing some interesting work on optimising hardware adders. Until I spoke with him, I didn’t realise how important this basic digital building block really is. An interesting statistic from his presentation slides:

When a RISC-V processor boots into Linux, 65% to 72% of instructions use addition.

By default, Yosys will synthesise something like this:

reg [31:0] a;

reg [31:0] b;

wire sum = a + b;

Using a ‘middle of the road’ adder, that gives medium PPA (power, performance, area) results. Teo has made a Python library and Yosys plugin that allows us to choose between 4 other types of adder:

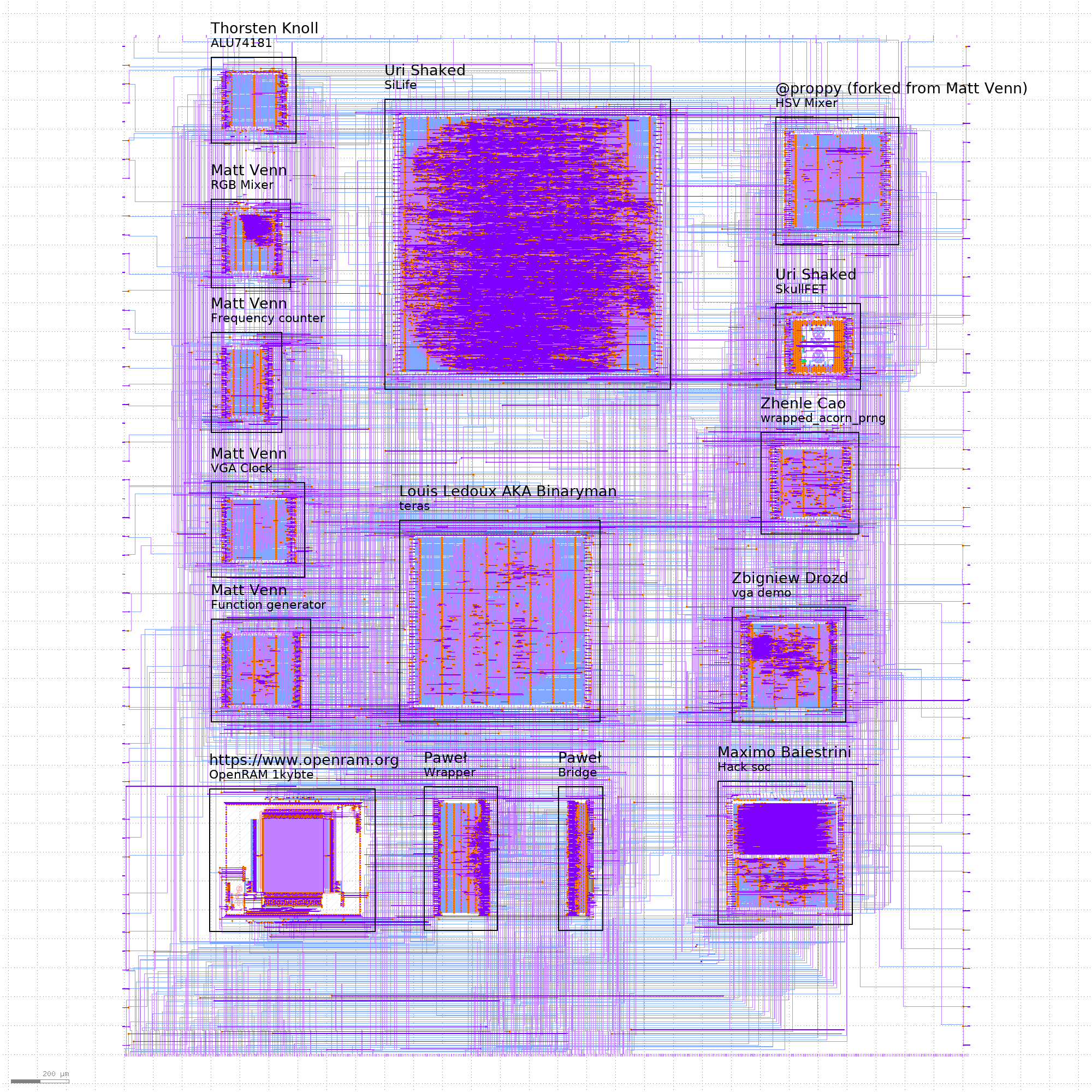

MPW5 submitted!

We submitted for MPW5!

We had 8 submissions from the course, the shared SRAM infrastructure, and I updated my demo designs.

We also had some people from the course make personal applications for a whole chip:

- Steve & Zhenle - PSRAM (HyperRAM) interface with an ACORN PRNG,

- Q3K - simple, microcontroller-style SoC based around a Lanai core,

- Maximo - Hardware implementation of the Hack Computer from the Nand to Tetris courses,

- Zbigniew - A rendering circuit for three blobs and a playable tetris clone.

And thanks to Paweł for updating the shared SRAM blocks.

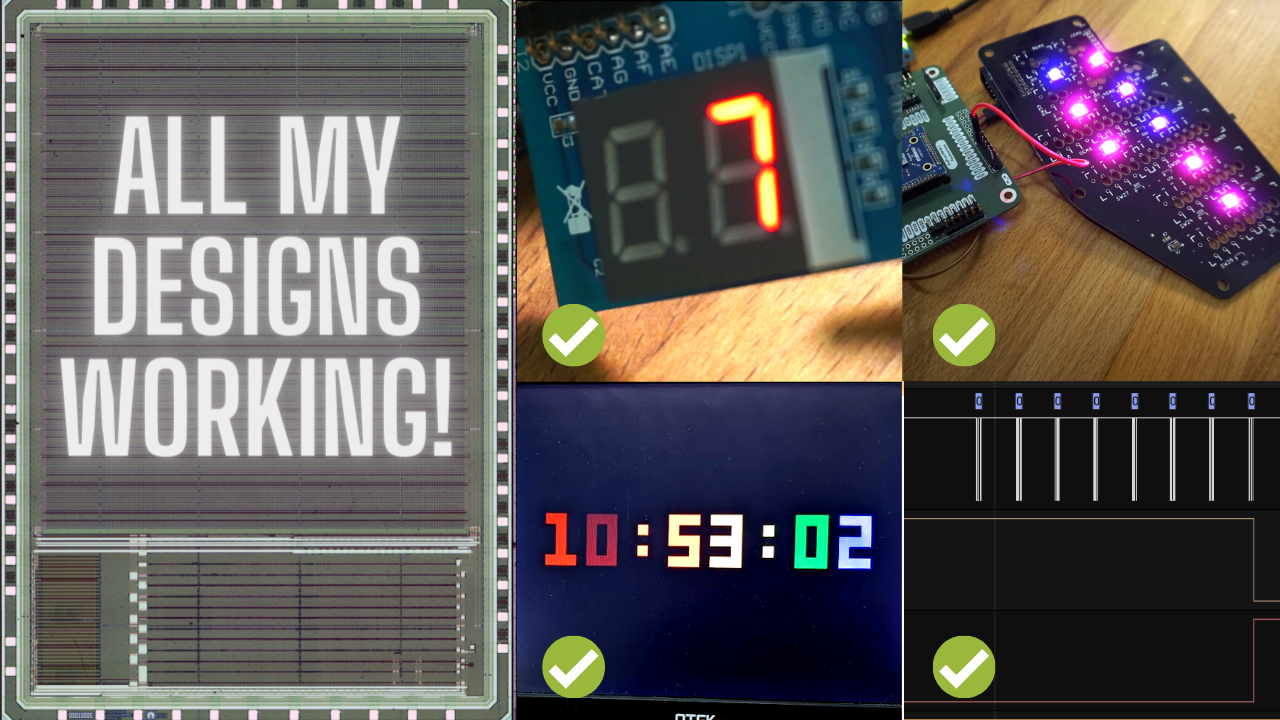

MPW1 is Alive

Yes! All the designs I submitted to MPW1 are working:

- ✅ 7 segment display

- ✅ TPM2137 CTF

- ✅ WS2812 led driver

- ✅ VGA clock

- ✅ Multiplexor

I put together a video to demonstrate them all:

The 4 other designs that were part of this submission were made by friends who I’ve now sent samples to. It’s looking likely that everyone’s designs will work.

MPW1 Bringup

I submitted my first ASIC designs to the free Google shuttle in December of 2020.

In October 2021, we heard there were serious clock related problems with the management area of the chip due to issues with the toolchain. It seemed unlikely that anyone would be able to get anything beyond a single blinking LED from MPW1. The hold violations in the management system meant that the PicoRV32 cpu couldn’t run and setup the GPIOs. So even if our designs work, we can’t get access to them.

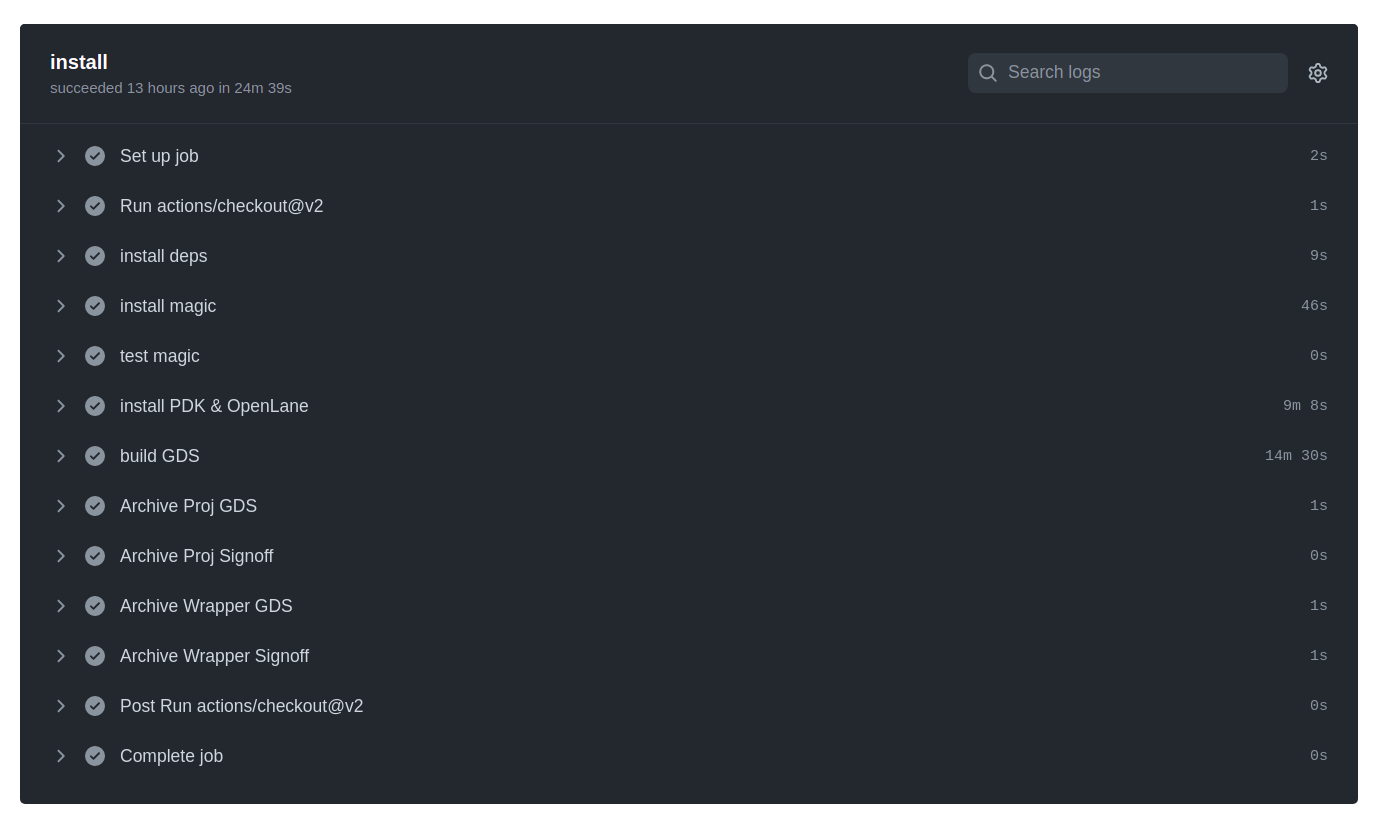

CI with Github Actions

I have slowly been learning how to use Github actions to help me build microchips.

It’s harder than it should be to get a working toolchain up. There are lots of repositories, submodules, docker images, environment variables, and they all have to be exactly right. If not, either the flow won’t work correctly, or you’ll make some GDS that will fail the precheck or tapeout tests.

For the course, I have a VM and a set of instructions to do a manual install.

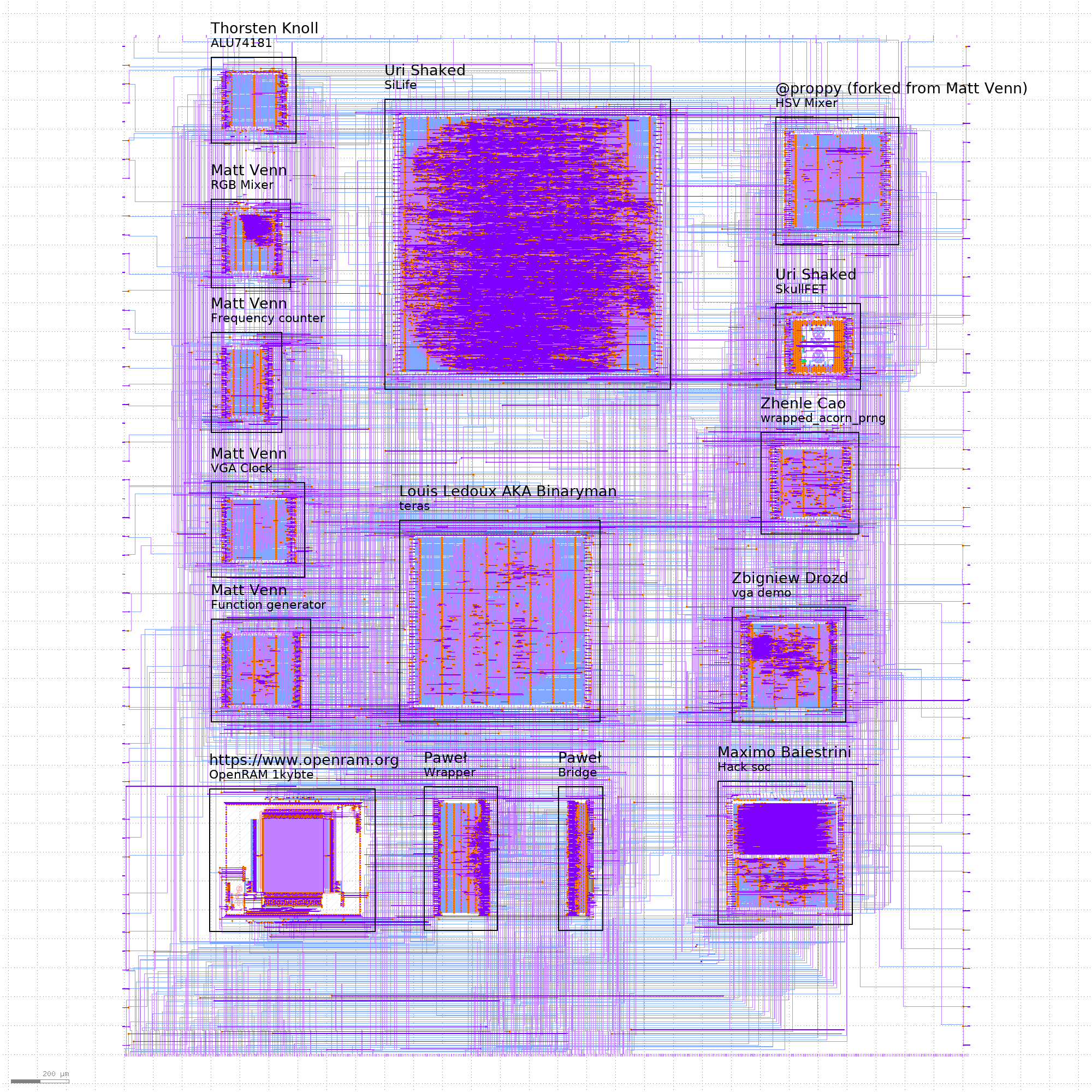

MPW4 submitted!

We submitted for MPW4! I was pretty pleased we managed to get so much in with such little time and for a tapeout date of New Year’s Eve.

We had 9 submissions from the course, with 1 demo project from me and a new version of Maximo’s hacksoc. Uri submitted 3 designs including some custom standard cells in the shape of skulls!

We also implemented the shared SRAM, which means that the group projects have access to a local fast memory (like a blockram on an FPGA).