Short articles about my experience with making ASICs, interviews and any other related topics I think are interesting.

MPW3 submitted!

We submitted for MPW3! The tapeout date was delayed by a couple of weeks due to issues with the toolchain.

Update!

We received silicon in June 2023 (18 months later!) and I was able to get both my designs partially working.

MPW3

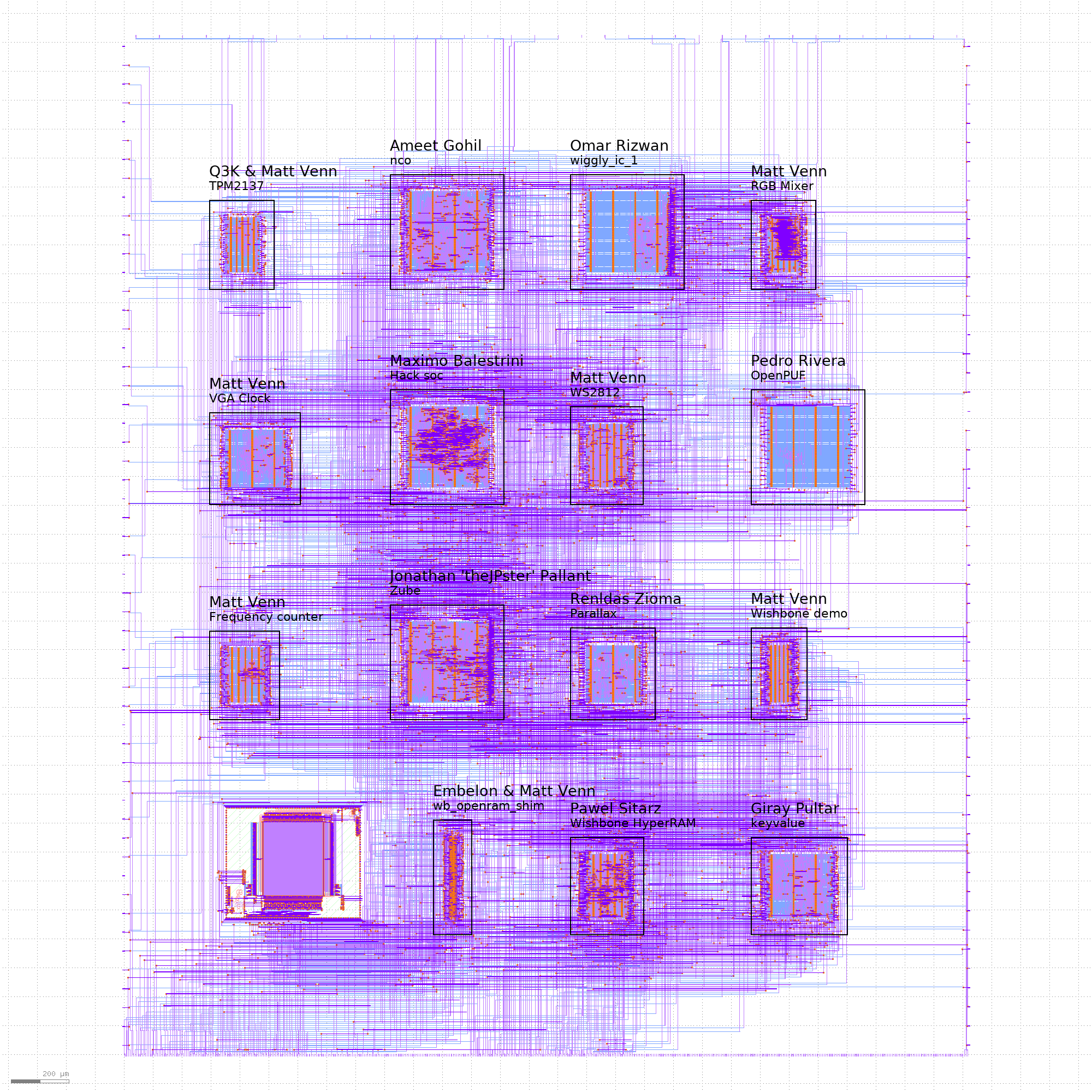

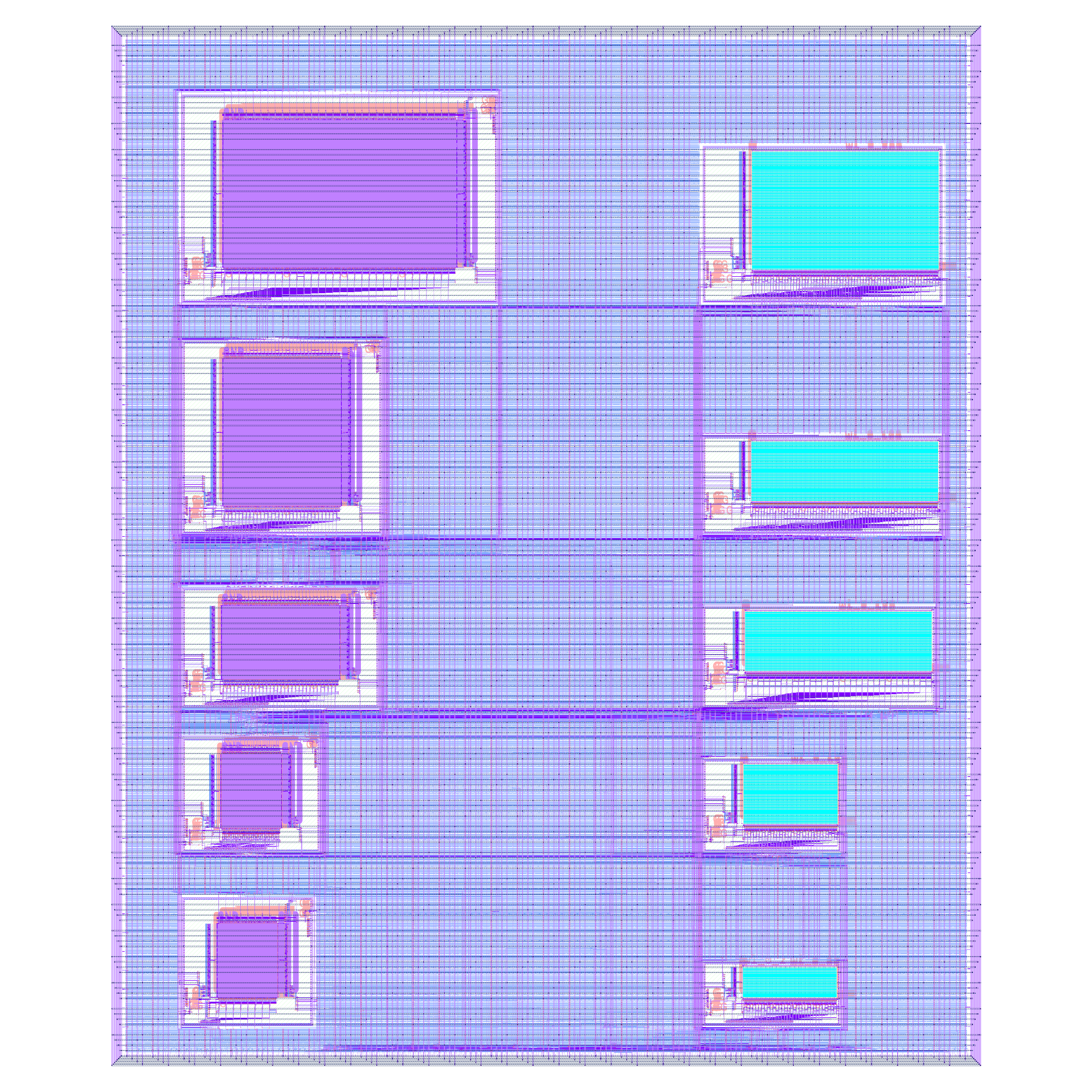

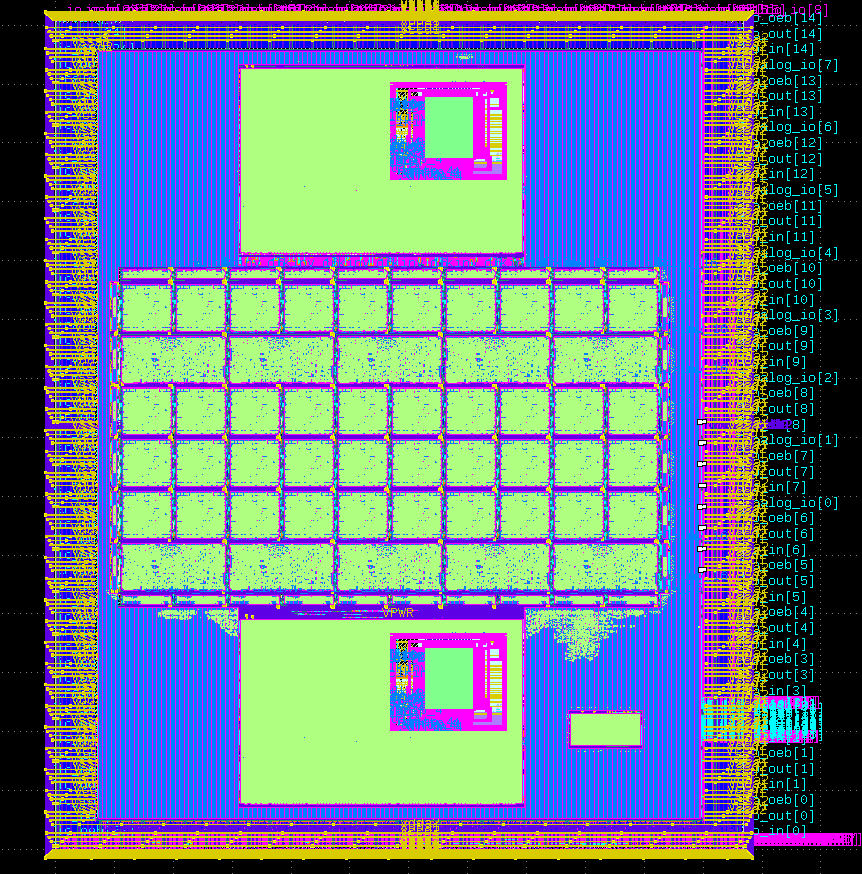

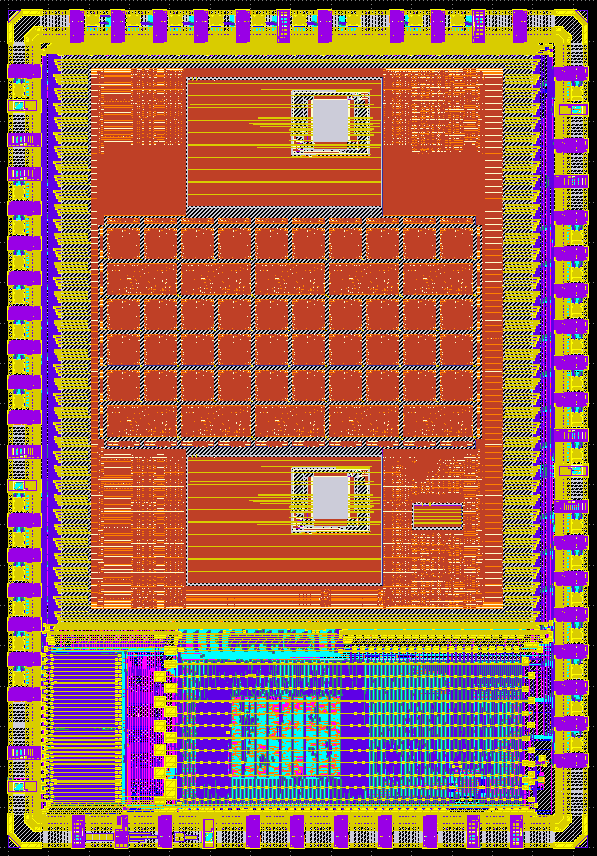

We had 7 new submissions from the course, 4 repeats from MPW1 and 2 with fixed clock trees, a new wishbone demo from me and the OpenRAM block.

MPW1 silicon has serious problems

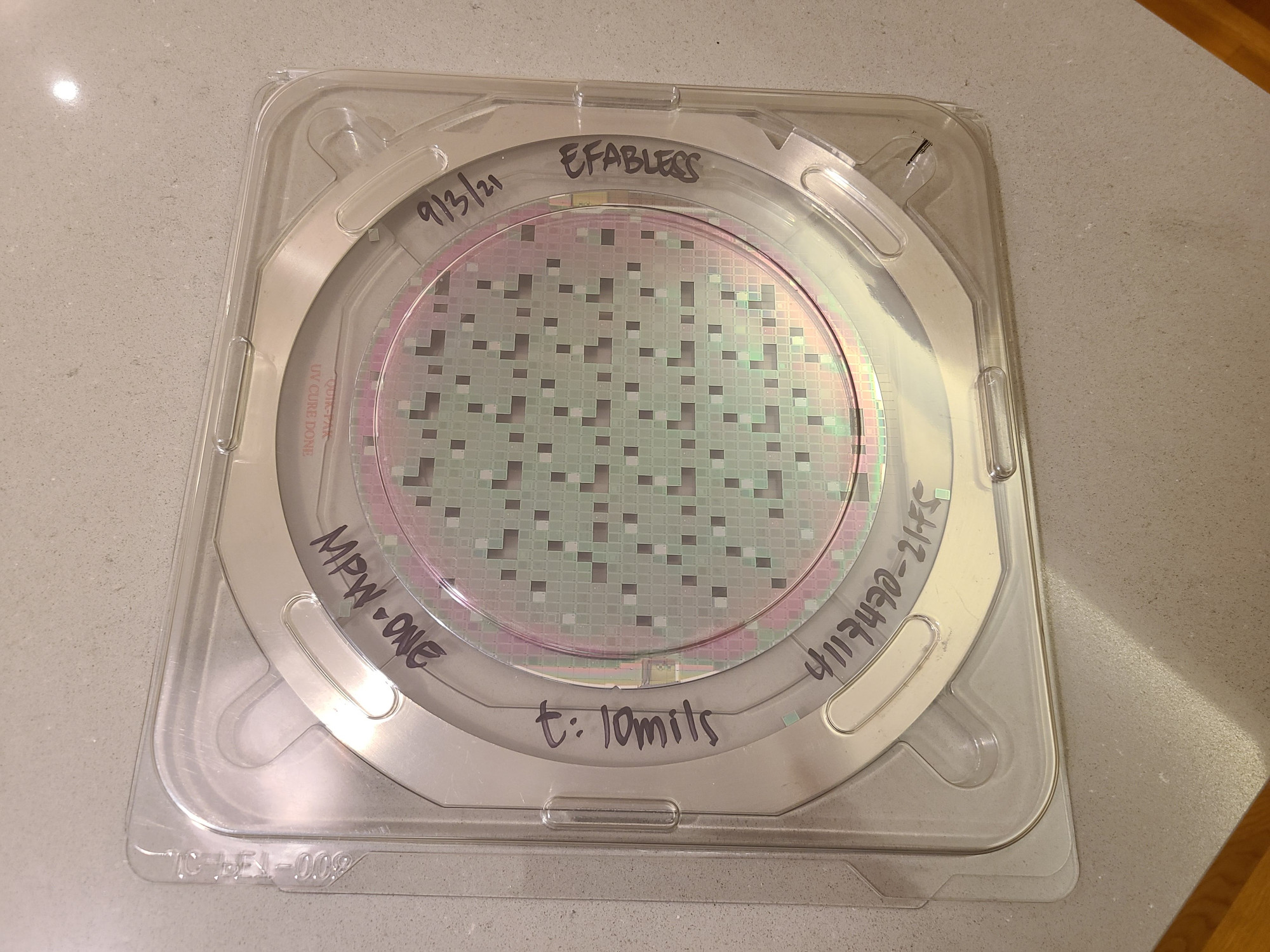

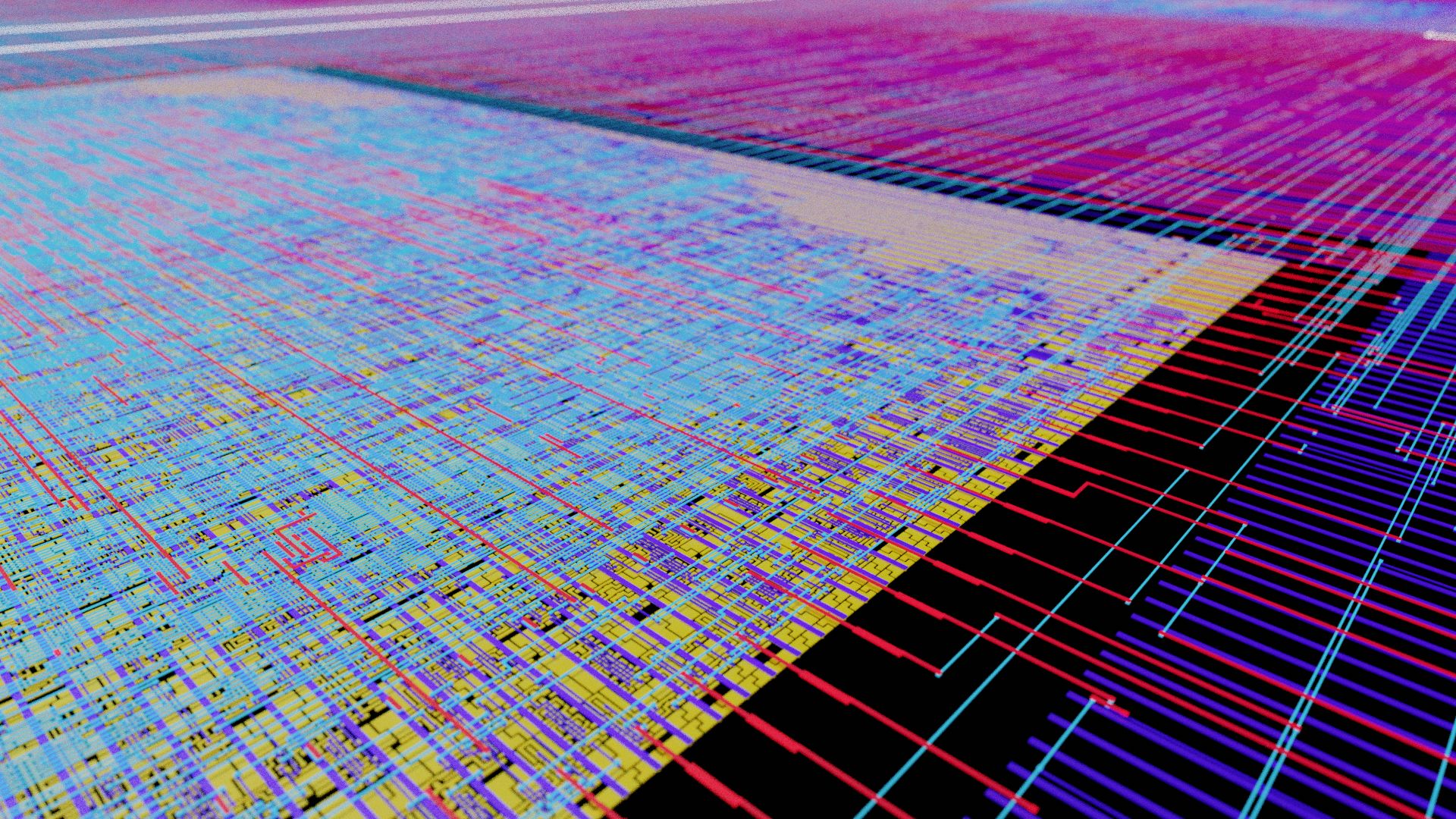

MPW1 seems an age ago, we submitted in December 2020, but it needed some last minute DRC fixes in February.

Silicon was received a few weeks ago, and unfortunately we have some serious issues that will prevent most designs from working. This appears to be due to a bad clock tree in the management section of the chip. Additionally, OpenSTA, the tool meant to verify the clock tree was also misconfigured.

The initial announcement is here.

Interview With Matt Guthaus

In this interview with Matt Guthaus, we talk about:

- Recap - what is OpenRAM

- Why do we need a memory compiler like OpenRAM?

- 3 phases of OpenRAM development

- What’s changed since FOSSi dialup

- MPW2 tapeout of OpenRAM

- Test modes

- What was hard about MPW2

- DRC issues

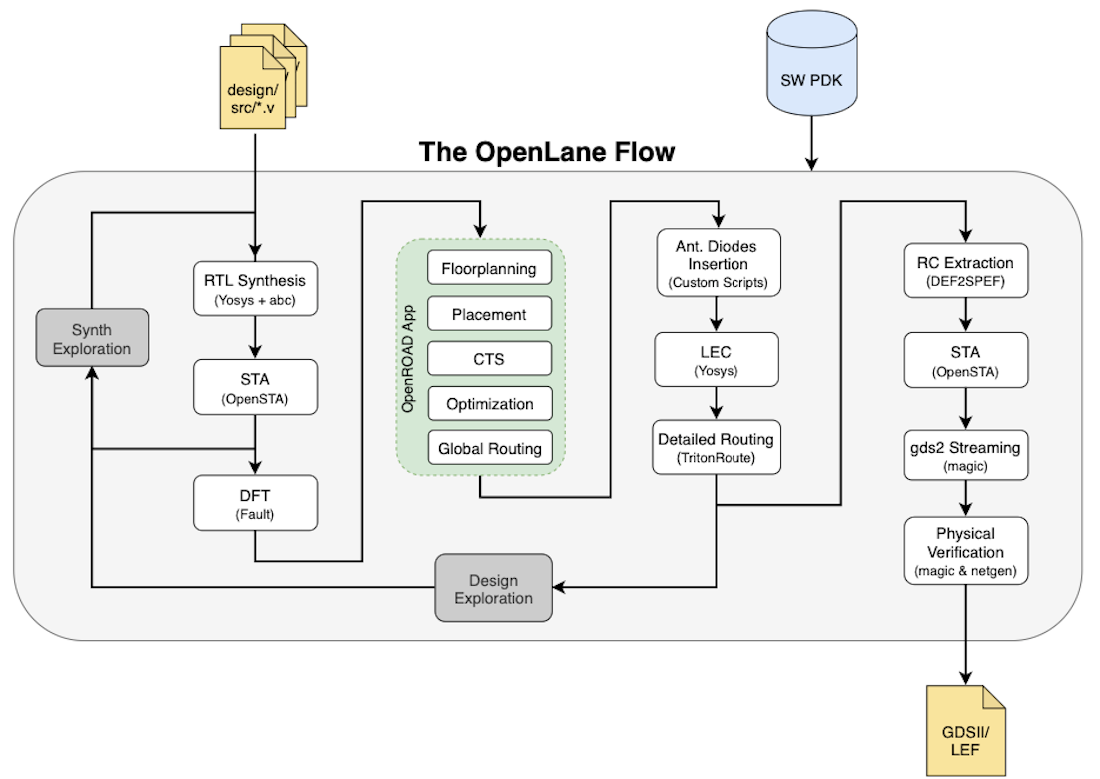

- Status of OpenLANE support for OpenRAM

- Future plans for OpenRAM

- Access to resistive RAM, hopefully for MPW4

Resources

- WOSET link: https://woset-workshop.github.io/

- MPW2 application: https://platform.efabless.com/projects/187

- FOSSi dialup on OpenRAM: https://www.youtube.com/watch?v=9Lw83kFtnc4

Interview With Tom Spyrou

Tom Spyrou is a long time EDA developer who has worked at large and small companies.

- In 1988 Developed QTV at VLSI technology. It was the first STA engine to be trusted to sign off devices for fabrication without timing based simulation.

- He was the original architect of PrimeTime STA algorithm.

- Manager of Cadence Common timing Engine and precursor to Open Access

- Senior technical positions at Synopsys, Cadence, Simplex, AMD, Altera and Intel.

Since 2019 he has been the Chief Architect and Technical Project Manager of OpenROAD since 2019.

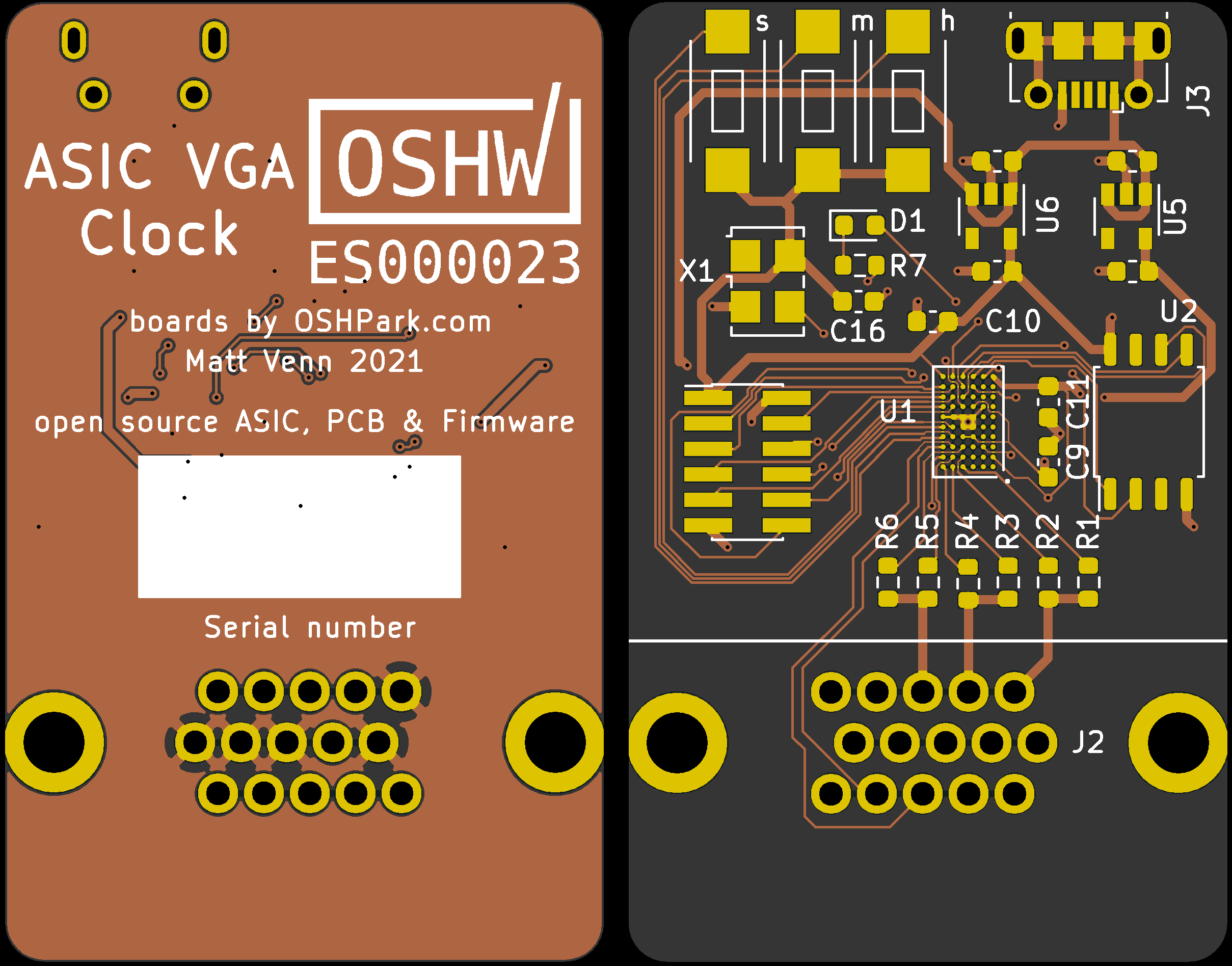

World's first certified open source hardware down to the chip level?

I’m very pleased to get OSHWA certification for my ASIC clock. I’m pretty sure this is the world’s first certified open source hardware down to the chip level!

Update! The PCB has been updated here.

The clock was submitted as part of MPW1. We’re expecting silicon back in August/September, so it was time to get the PCB ready and try to source the other components!

I started off by forking Sam Littlewood’s carrier board. This is a 4 layer board, but as I don’t need all the signals I was able to get it down to 2 layers for cheaper fabrication. OSHPark have sponsored the board in their special ‘after dark’ finish.

Interview With Dirk Koch and Nguyen Dao

One of the popular types of entries to MPW1 & 2 have been FPGAs. I have previously spoken with Arya Reais-Parsi about their FPGA project submitted to MPW1.

In MPW2 I noticed there were a couple of applications that seemed fairly advanced - especially FuseRISC: 2 RISCV processors with embedded FPGA fabric between them.

Dirk & Nguyen kindly allowed me to interview them about:

- their FABulous eFPGA framework,

- support for Yosys & NextPNR,

- parameterisation of the fabric,

- blockrams with OpenRAM,

- their MPW applications and previous tape-outs, and

- their experience with the open source tools.

Enjoy!

Course Improvements

After 6 months, 90 participants and 14 designs submitted to MPW2, I’m making the Zero to ASIC course even better!

One of the things that’s great about the course is that you can proceed at your own pace. I originally set the course length at 6 weeks, but a lot of people want more time than this. To resolve this I have:

- removed the expiry date on the discord support,

- removed the expiry date on office hours.

To help grow the community and provide another venue for discussing the course, I have added a weekly group call for anyone on the course to join. It’s been going really well; we answer questions, discuss the course and chat about what’s going on in the world of open source ASICs.

Livestream with Thomas Parry: analogue design with the open source ASIC tools

There continues to be a lot of interest about analogue design with the open source PDK.

To cover this interest, I’ve previously interviewed:

One of the big changes in MPW2 was the provision of more analogue support in the form of Caravan - a new harness. This is exciting because one of the key advantages of an ASIC over an FPGA is the mixed signal capability.

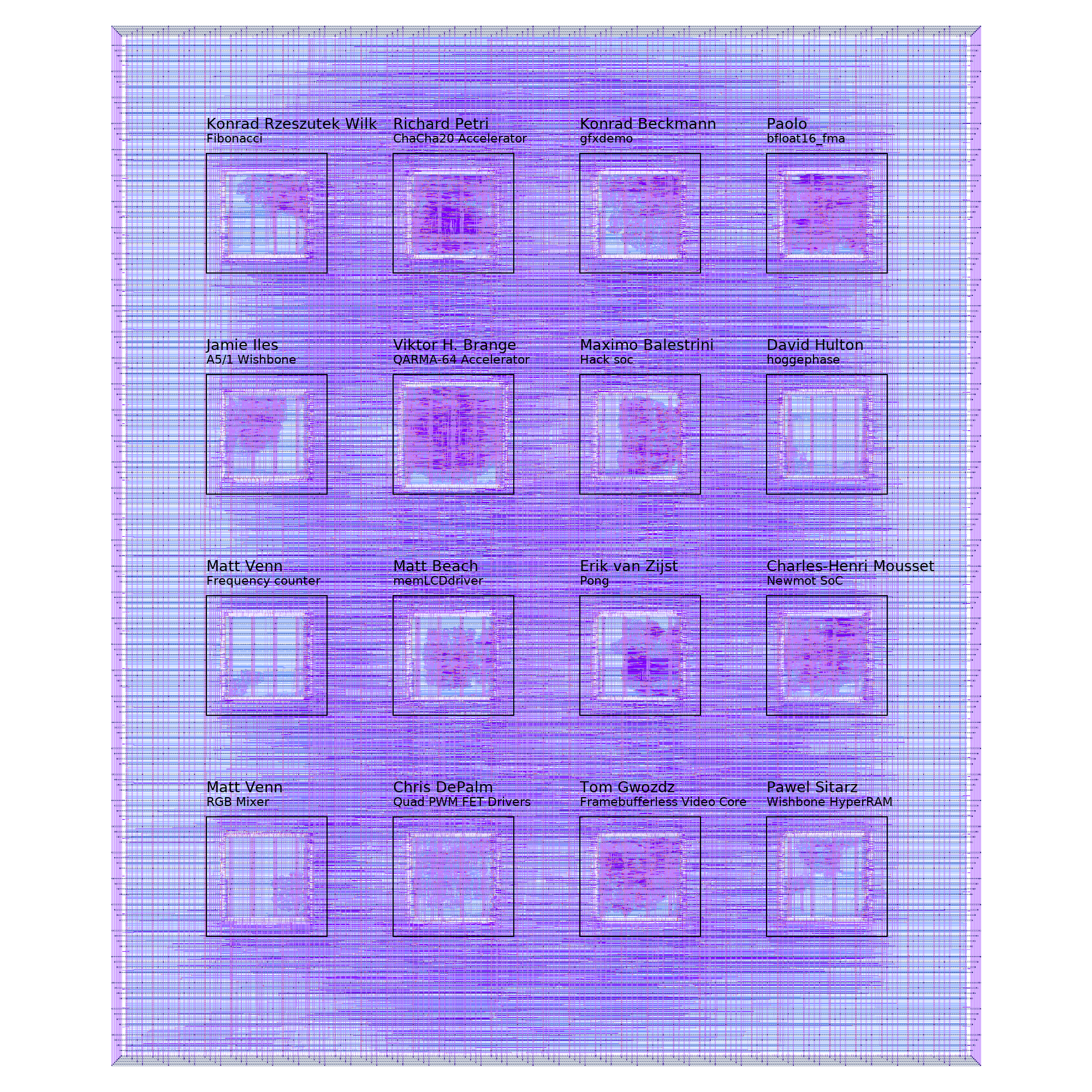

MPW2 Submitted

We did it! 14 people from the course got their designs into the group submission, and the project was accepted for fabrication. Silicon here we come!

You can get all the details on all the projects submitted to MPW2 here - you’ll need to select the MPW2 filter.

And see how I put the application together here, with the repo here.

Project listing

RGB Mixer

- Author: Matt Venn

- Github: https://github.com/mattvenn/wrapped_rgb_mixer/tree/caravel-mpw-two-c

- Description: reads 3 encoders and generates PWM signals to drive an RGB LED

Frequency counter

- Author: Matt Venn

- Github: https://github.com/mattvenn/wrapped_frequency_counter/tree/caravel-mpw-two-c

- Description: Counts pulses on input and displays frequency on 2 seven segment displays

A5/1 Wishbone

- Author: Jamie Iles

- Github: https://github.com/jamieiles/a5-1-wb-macro

- Description: A5/1 cryto block connected via wishbone to PicoRV32

Fibonacci

- Author: Konrad Rzeszutek Wilk

- Github: https://github.com/konradwilk/fibonacci

- Description: Fibonacci emitter connected to [37:8] and controlled via wishbone

Quad PWM FET Drivers

- Author: Chris DePalm

- Github: https://github.com/ChrisDePalm/wrapped_quad_pwm_fet_drivers.git

- Description: 4 PWM FET Drivers for Power Applications

memLCDdriver

- Author: Matt Beach

- Github: https://github.com/matt-beach/wrapped_memLCDdriver.git

- Description: SPI to 64-color memory LCD interface

QARMA-64 Accelerator

- Author: Viktor H. Brange

- Github: https://github.com/vbrange/verilog_qarma

- Description: Implementation of QARMA 64

ChaCha20 Accelerator

- Author: Richard Petri

- Github: https://github.com/rpls/wrapped_chacha_wb_accel

- Description: A minimal Wishbone connected ChaCha20 accelerator

Framebufferless Video Core

- Author: Tom Gwozdz

- Github: https://github.com/tomgwozdz/fbless-graphics-core

- Description: A framebufferless VGA video generator, under CPU control

Pong

- Author: Erik van Zijst

- Github: https://github.com/erikvanzijst/wrapped_pong.git

- Description: A hardware implementation of Pong

Hack soc

- Author: Maximo Balestrini

- Github: https://github.com/mbalestrini/wrapped_hack_soc

- Description: Hardware implementation of the Hack Computer from the Nand to Tetris courses

gfxdemo

- Author: Konrad Beckmann

- Github: https://github.com/kbeckmann/wrapped_gfxdemo

- Description: gfxdemo

Wishbone HyperRAM

- Author: Pawel Sitarz

- Github: https://github.com/embelon/wrapped_wb_hyperram

- Description: Simple HyperRAM driver accesible on Wishbone bus

Newmot SoC

- Author: Charles-Henri Mousset

- Github: https://github.com/chmousset/caravel_multi_newmot

- Description: Simple SoC dmonstrating a Stepper Motor step/dir generator, and litex wishbone / uart / pwm

hoggephase

- Author: David Hulton

- Github: https://github.com/h1kari/wrapped_hoggephase_project

- Description: Hogge Phase EMFI/BBI Glitch Detector

bfloat16_fma

- Author: Author

- Github: https://github.com/etalian/mensa

- Description: dual bfloat16 fused multiply-add

Multi project tools

This time around submission was a lot easier and nerve-wracking than MPW1.

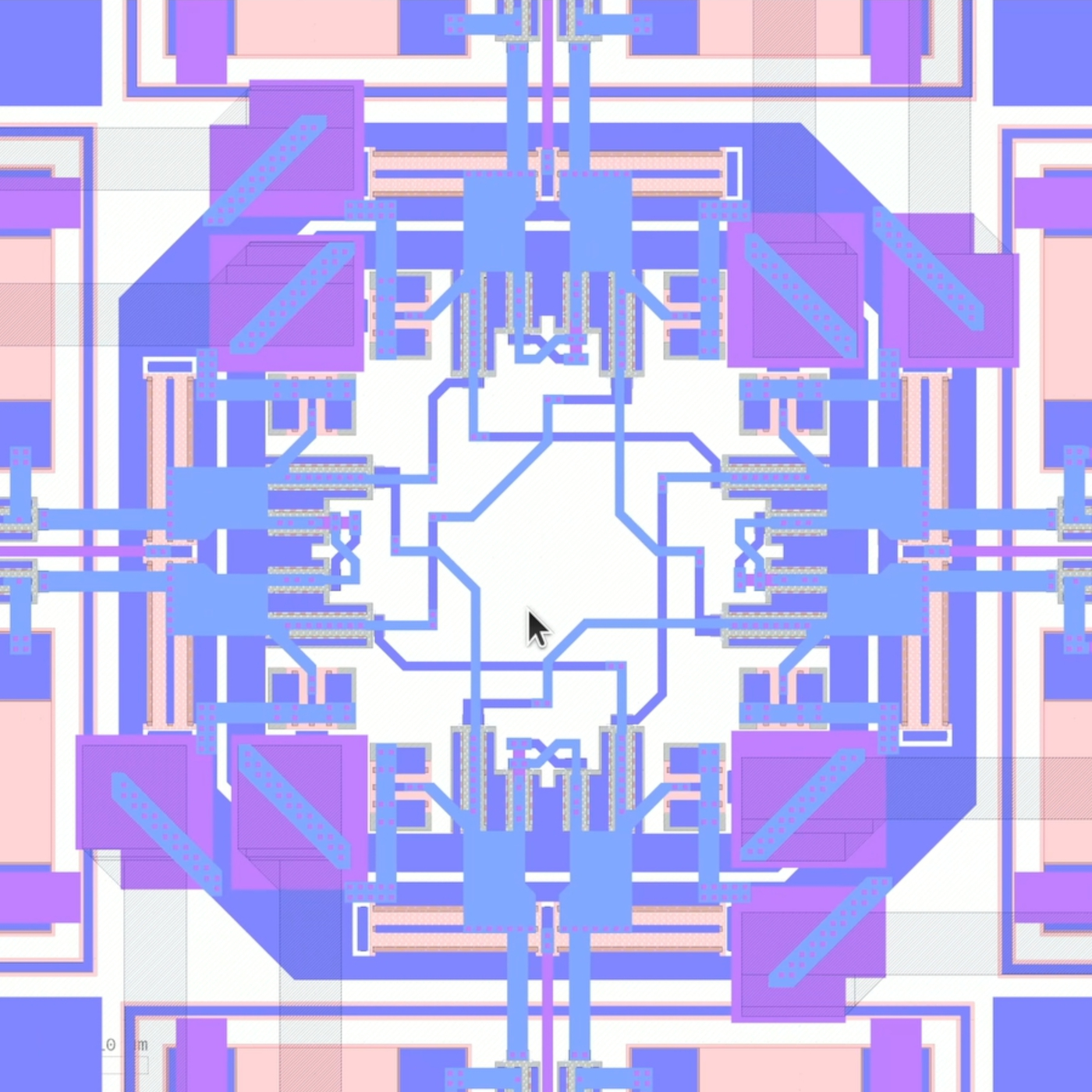

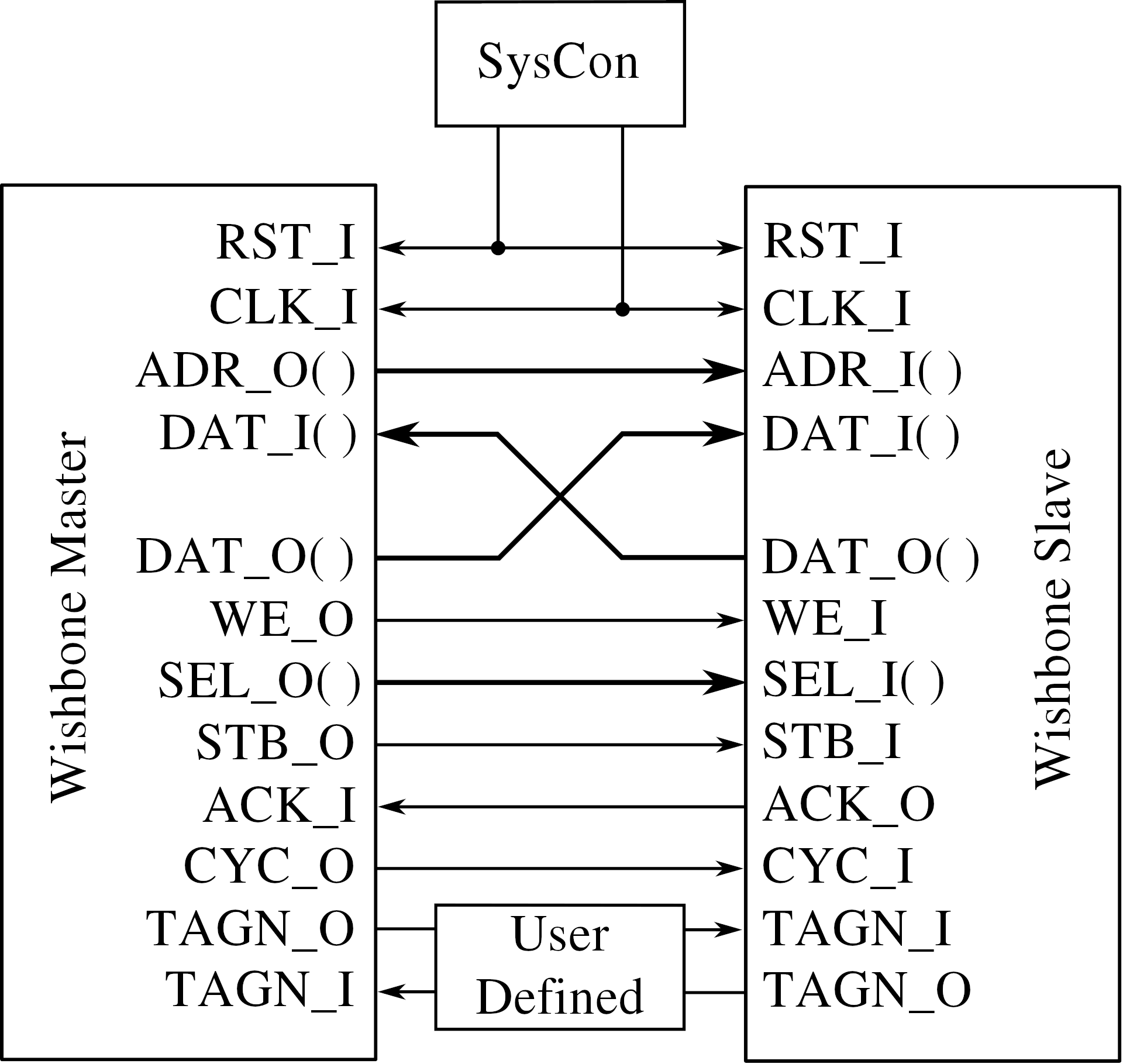

Caravel Wishbone Demo

Caravel is the name of the harness provided by Efabless to make it easier to submit a design to the foundry.

Among other things, it provides:

- The padring

- 3kB of memory

- A small RISCV processor called PicoRV32

- GPIOs

- A logic analyser

- A Wishbone bus

For the full details, check the documentation

The simplest way to interface between your project and the PicoRV32 is probably the logic analyser. This gives you 128 ins and outs that you can use to configure or debug your design.